- Altera Manuals

- Computer Hardware

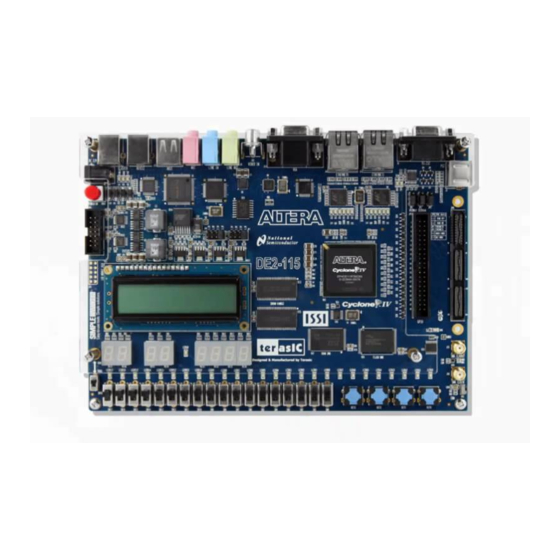

- tPad DE2-115

- User manual

Altera DE2-115 User Manual

- User manual (43 pages)

- page of 116 Go / 116

Table of Contents

Chapter 7 appendix, chapter 1 de2-115 package.

- Package Contents

- The DE2-115 Board Assembly

- Getting Help

Chapter 2 Introduction of the Altera DE2-115 Board

- Layout and Components

- Block Diagram of the DE2-115 Board

- Power-Up the DE2-115 Board

Chapter 3 DE2-115 Control Panel

- Control Panel Setup

- Controlling the Leds, 7-Segment Displays and LCD Display

- Switches and Push-Buttons

- Sdram/Sram/Eeprom/Flash Controller and Program-Mer

- USB Monitoring

- PS/2 Device

- Communication

- IR Receiver

- Overall Structure of the DE2-115 Control Panel

Chapter 4 Using the DE2-115 Board

- Configuring the Cyclone IV E FPGA

- Using Push-Buttons and Switches

- Using the 7-Segment Displays

- Clock Circuitry

- Using the LCD Module

- High Speed Mezzanine Card

- Using the Expansion Header

- Using 14-Pin General Purpose I/O Connector

- Using the 24-Bit Audio CODEC

- Serial Port

- PS/2 Serial Port

- Gigabit Ethernet Transceiver

- Implementing a TV Encoder

- Using the USB Interface

- Using SRAM/SDRAM/FLASH/EEPROM/SD Card

Chapter 5 DE2-115 System Builder

- Introduction

- General Design Flow

- Using DE2-115 System Builder

- System Configuration

Chapter 6 Examples of Advanced Demonstrations

- DE2-115 Factory Configuration

- TV Box Demonstration

- USB Paintbrush

- A Karaoke Machine

- SD Card Demonstration

- SD Card Music Player

- PS/2 Mouse Demonstration

- IR Receiver Demonstration

- Music Synthesizer Demonstration

- Audio Recording and Playing

- Web Server Demonstration

- Revision History

- Copyright Statement

Advertisement

Quick Links

- 1 Layout and Components

- 2 Controlling the Leds, 7-Segment Displays and Lcd Display

- 3 Switches and Push-Buttons

- 4 Using Push-Buttons and Switches

- 5 Using Leds

- 6 Using the 7-Segment Displays

- Download this manual

Related Manuals for Altera DE2-115

Summary of Contents for Altera DE2-115

Page 2: table of contents.

- Page 3 Chapter 5 DE2-115 System Builder ..............70 5.1 Introduction ............................70 5.2 General Design Flow .......................... 70 5.3 Using DE2-115 System Builder ......................71 Chapter 6 Examples of Advanced Demonstrations ..........77 6.1 DE2-115 Factory Configuration ......................77 6.2 TV Box Demonstration ........................78 6.3 USB Paintbrush ..........................

Page 4: Chapter 7 Appendix

Page 5: de2-115 package.

- Page 6 Bag of six rubber (silicon) covers for the DE2-115 board stands. The bag also contains some extender pins, which can be used to facilitate easier probing with testing equipment of the board‟s I/O expansion headers. Clear plastic cover for the board.

Page 7: Getting Help

Page 8: introduction of the altera de2-115 board.

- Page 9 Figure 2-2 The DE2-115 board (bottom view) The DE2-115 board has many features that allow users to implement a wide range of designed circuits, from simple circuits to various multimedia projects. The following hardware is provided on the DE2-115 board: ...

Page 10: Block Diagram Of The De2-115 Board

- Page 11 Following is more detailed information about the blocks in Figure 2-3: Cyclone IV EP4CE115F29 device 114,480 LEs 432 M9K memory blocks 3,888 Kbits embedded memory 4 PLLs JTAG and AS mode configuration EPCS64 serial configuration device ...

- Page 12 40-pin expansion port o Configurable I/O standards (voltage levels:3.3/2.5/1.8/1.5V) VGA-out connector o VGA DAC (high speed triple DACs) DB9 serial connector for RS-232 port with flow control PS/2 mouse/keyboard Three 50MHz oscillator clock inputs SMA connectors (external clock input/output) ...

Page 13: Power-Up The De2-115 Board

- Page 14 You can also connect a microphone to the microphone-in connector on the DE2-115 board; your voice will be mixed with the music playing on the audio player Figure 2-4 The default VGA output pattern...

Page 15: De2-115 Control Panel

- Page 16 LEDs and observing the result on the DE2-115 board. Figure 3-1 The DE2-115 Control Panel 3-2. The “Control Circuit” that The concept of the DE2-115 Control Panel is illustrated in Figure performs the control functions is implemented in the FPGA board. It communicates with the Control Panel window, which is active on the host computer, via the USB Blaster link.

Page 17: Controlling The Leds, 7-Segment Displays And Lcd Display

- Page 18 Figure 3-4. From the window, directly use the left-right arrows to control the 7-SEG patterns on the DE2-115 board which are updated immediately. Note that the dots of the 7-SEGs are not enabled on DE2-115 board. Figure 3-4 Controlling 7-SEG display...

Page 19: Switches And Push-Buttons

Page 20: sdram/sram/eeprom/flash controller and program-mer.

- Page 21 Figure 3-7 Accessing the SDRAM A 16-bit word can be written into the SDRAM by entering the address of the desired location, specifying the data to be written, and pressing the Write button. Contents of the location can be read by pressing the Read button.

Page 22: Usb Monitoring

Page 23: ps/2 device, page 24: sd card, page 25: vga, page 26: hsmc, page 27: ir receiver, page 28: overall structure of the de2-115 control panel.

- Page 29 Figure 3-15 The block diagram of the DE2-115 control panel...

Page 30: Using The De2-115 Board

- Page 31 The sections below describe the steps used to perform both JTAG and AS programming. For both methods the DE2-115 board is connected to a host computer via a USB cable. Using this connection, the board will be identified by the host computer as an Altera USB Blaster device. The process for installing on the host computer the necessary software device driver that communicates with the USB Blaster is described in the tutorial “Getting Started with Altera’s DE2-115 Board”...

- Page 32 Configure the JTAG programming circuit by setting the RUN/PROG slide switch (SW19) to the RUN position (See Figure 4-4) Connect the supplied USB cable to the USB Blaster port on the DE2-115 board (See Figure 2-1) The FPGA can now be programmed by using the Quartus II Programmer to select a configuration bit stream file with the .sof filename extension...

Page 33: Using Push-Buttons And Switches

- Page 34 Schmitt Trigger Debounced Figure 4-7 Switch debouncing There are also 18 slide switches on the DE2-115 board (See Figure 4-8). These switches are not debounced, and are assumed for use as level-sensitive data inputs to a circuit. Each switch is connected directly to a pin on the Cyclone IV E FPGA.

Page 35: Using Leds

- Page 36 Table 4-1 Pin Assignments for Slide Switches Signal Name FPGA Pin No. Description I/O Standard SW[0] PIN_AB28 Slide Switch[0] Depending on JP7 SW[1] PIN_AC28 Slide Switch[1] Depending on JP7 SW[2] PIN_AC27 Slide Switch[2] Depending on JP7 SW[3] PIN_AD27 Slide Switch[3] Depending on JP7 SW[4] PIN_AB27...

Page 37: Using The 7-Segment Displays

- Page 38 HEX0[5] PIN_J22 Seven Segment Digit 0[5] Depending on JP7 HEX0[6] PIN_H22 Seven Segment Digit 0[6] Depending on JP7 HEX1[0] PIN_M24 Seven Segment Digit 1[0] Depending on JP7 HEX1[1] PIN_Y22 Seven Segment Digit 1[1] Depending on JP7 HEX1[2] PIN_W21 Seven Segment Digit 1[2] Depending on JP7 HEX1[3] PIN_W22...

Page 39: Clock Circuitry

Page 40: using the lcd module, page 41: high speed mezzanine card.

- Page 42 I/O standard between DE2-115 HSMC connector pins and daughter card system. For example, if the I/O standard of HSMC pins on DE2-115 board is set to 1.8V, a daughter card with 3.3V I/O standard may not work properly on DE2-115 board due to I/O standard mismatch.

- Page 43 Figure 4-14 LVDS interface on HSMC connector and Cyclone IV E FPGA Table 4-9 Pin Assignments for HSMC connector FPGA Pin Signal Name Description I/O Standard HSMC_CLKIN0 PIN_AH15 Depending Dedicated clock input on JP6 HSMC_CLKIN_N1 PIN_J28 Depending LVDS RX or CMOS I/O or differential clock input on JP7 HSMC_CLKIN_N2 PIN_Y28...

- Page 44 on JP7 HSMC_RX_D_N[1] PIN_C27 Depending LVDS RX bit 1n or CMOS I/O on JP7 HSMC_RX_D_N[2] PIN_E26 Depending LVDS RX bit 2n or CMOS I/O on JP7 HSMC_RX_D_N[3] PIN_G26 Depending LVDS RX bit 3n or CMOS I/O on JP7 HSMC_RX_D_N[4] PIN_H26 Depending LVDS RX bit 4n or CMOS I/O on JP7...

- Page 45 HSMC_RX_D_P[7] PIN_M25 Depending LVDS RX bit 7 or CMOS I/O on JP7 HSMC_RX_D_P[8] PIN_R25 Depending LVDS RX bit 8 or CMOS I/O on JP7 HSMC_RX_D_P[9] PIN_T25 Depending LVDS RX bit 9 or CMOS I/O on JP7 HSMC_RX_D_P[10] PIN_U25 Depending LVDS RX bit 10 or CMOS I/O on JP7 HSMC_RX_D_P[11] PIN_L21 Depending...

Page 46: Using The Expansion Header

- Page 47 GND pins. Figure 4-15 shows the I/O distribution of the GPIO connector. The maximum power consumption of the daughter card that connects to GPIO port is shown in Table 4-10. Figure 4-15 GPIO Pin Arrangement Table 4-10 Power Supply of the Expansion Header Supplied Voltage Max.

- Page 48 The voltage level of the I/O pins on the expansion headers can be adjusted to 3.3V, 2.5V, 1.8V, or 1.5V using JP6 (The default value is 3.3V, see Figure 4-17). Because the expansion I/Os are connected to Bank 4 of the FPGA and the VCCIO voltage (VCCIO4) of this bank is controlled by the header JP6, users can use a jumper to select the input voltage of VCCIO4 to 3.3V, 2.5V, 1.8V, and 1.5V to control the voltage level of the I/O pins.

- Page 49 I/O standard between DE2-115 GPIO connector pins and daughter card system. For example, if the I/O standard of GPIO pins on DE2-115 board is set to 1.8V, a daughter card with 3.3V I/O standard may not work properly on the DE2-115 board due to I/O standard mismatch.

- Page 50 Figure 4-19 Using Emulated LVDS on GPIO Table 4-12 Pin Assignments for Expansion Headers Signal Name FPGA Pin No. Description I/O Standard GPIO[0] PIN_AB22 GPIO Connection DATA[0] Depending on JP6 GPIO[1] PIN_AC15 GPIO Connection DATA[1] Depending on JP6 GPIO[2] PIN_AB21 GPIO Connection DATA[2] Depending on JP6 GPIO[3]...

Page 51: Using 14-Pin General Purpose I/O Connector

Page 52: using vga.

- Page 53 Note: The RGB data bus on DE2-115 board is 8 bit instead of 10 bit on DE2/DE2-70 board. Figure 4-22 VGA horizontal timing specification Table 4-14 VGA Horizontal Timing Specification VGA mode Horizontal Timing Spec Configuration Resolution(HxV) a(us) b(us) c(us)

Page 54: Using The 24-Bit Audio Codec

Page 55: serial port, page 56: ps/2 serial port, page 57: gigabit ethernet transceiver.

- Page 58 You will need to perform a hardware reset after any change for enabling new settings. Table 4-21 Table 4-22 describe the working mode settings for ENET0 PHY (U8) and ENET1 PHY (U9) respectively. In addition, it is dynamically configurable to support 10Mbps, 100Mbps (Fast Ethernet) or 1000Mbps (Gigabit Ethernet) operation using standard Cat 5e UTP cabling.

- Page 59 Table 4-22 Jumper Settings for Working Mode of ENET1 (U9) JP2 Jumper Settings ENET1 PHY Working Mode Short Pins 1 and 2 RGMII Mode Short Pins 2 and 3 MII Mode Table 4-23 Pin Assignments for Fast Ethernet Signal Name FPGA Pin No.

- Page 60 Ethernet clock source 3.3V The DE2-115 board is equipped with an Analog Device ADV7180 TV decoder chip. The ADV7180 is an integrated video decoder that automatically detects and converts a standard analog baseband television signals (NTSC, PAL, and SECAM) into 4:2:2 component video data compatible with the 8-bit ITU-R BT.656 interface standard.

Page 61: Tv Decoder

Page 62: using the usb interface, page 63: using ir, page 64: using sram/sdram/flash/eeprom/sd card.

- Page 65 Figure 4-34 Connections between FPGA and SDRAM FLASH The board is assembled with 8MB of flash memory using an 8-bit data bus. The device uses 3.3V CMOS signaling standard. Because of its non-volatile property, it is usually used for storing software binaries, images, sounds or other media.

- Page 66 Many applications use a large external storage device, such as SD Card or CF card, for storing data. The DE2-115 board provides the hardware needed for SD Card access. Users can implement custom controllers to access the SD Card in SPI mode and SD Card 4-bit or 1-bit mode.

- Page 67 Figure 4-37 Connections between FPGA and SD Card Socket Table 4-27 SRAM Pin Assignments Signal Name FPGA Pin No. Description I/O Standard SRAM_ADDR[0] PIN_AB7 SRAM Address[0] 3.3V SRAM_ADDR[1] PIN_AD7 SRAM Address[1] 3.3V SRAM_ADDR[2] PIN_AE7 SRAM Address[2] 3.3V SRAM_ADDR[3] PIN_AC7 SRAM Address[3] 3.3V SRAM_ADDR[4] PIN_AB6...

- Page 68 SRAM_DQ[7] PIN_AF7 SRAM Data[7] 3.3V SRAM_DQ[8] PIN_AD1 SRAM Data[8] 3.3V SRAM_DQ[9] PIN_AD2 SRAM Data[9] 3.3V SRAM_DQ[10] PIN_AE2 SRAM Data[10] 3.3V SRAM_DQ[11] PIN_AE1 SRAM Data[11] 3.3V SRAM_DQ[12] PIN_AE3 SRAM Data[12] 3.3V SRAM_DQ[13] PIN_AE4 SRAM Data[13] 3.3V SRAM_DQ[14] PIN_AF3 SRAM Data[14] 3.3V SRAM_DQ[15] PIN_AG3 SRAM Data[15]...

- Page 69 DRAM_DQ[16] PIN_M8 SDRAM Data[16] 3.3V DRAM_DQ[17] PIN_L8 SDRAM Data[17] 3.3V DRAM_DQ[18] PIN_P2 SDRAM Data[18] 3.3V DRAM_DQ[19] PIN_N3 SDRAM Data[19] 3.3V DRAM_DQ[20] PIN_N4 SDRAM Data[20] 3.3V DRAM_DQ[21] PIN_M4 SDRAM Data[21] 3.3V DRAM_DQ[22] PIN_M7 SDRAM Data[22] 3.3V DRAM_DQ[23] PIN_L7 SDRAM Data[23] 3.3V DRAM_DQ[24] PIN_U5 SDRAM Data[24]...

- Page 70 FL_ADDR[15] PIN_Y10 FLASH Address[15] 3.3V FL_ADDR[16] PIN_AA8 FLASH Address[16] 3.3V FL_ADDR[17] PIN_AH12 FLASH Address[17] 3.3V FL_ADDR[18] PIN_AC12 FLASH Address[18] 3.3V FL_ADDR[19] PIN_AD12 FLASH Address[19] 3.3V FL_ADDR[20] PIN_AE10 FLASH Address[20] 3.3V FL_ADDR[21] PIN_AD10 FLASH Address[21] 3.3V FL_ADDR[22] PIN_AD11 FLASH Address[22] 3.3V FL_DQ[0] PIN_AH8 FLASH Data[0]...

Page 71: Chapter 5 De2-115 System Builder

Page 72: using de2-115 system builder.

- Page 73 Input Project Name Input project name as show in Figure 5-3. Project Name: Type in an appropriate name here, it will automatically be assigned as the name of your top-level design entity. Figure 5-3 The DE2-115 Board Type and Project Name...

Page 74: System Configuration

- Page 75 The “Prefix Name” is an optional feature which denotes the prefix pin name of the daughter card assigned in your design. Users may leave this field empty. HSMC Expansion Users can connect HSMC-interfaced daughter cards onto HSMC located on the DE2-115 board shown in Figure 5-6.

- Page 76 The “Prefix Name” is an optional feature that denotes the pin name of the daughter card assigned in your design. Users may leave this field empty. Project Setting Management The DE2-115 System Builder also provides functions to restore default setting, loading a setting, and saving users‟ board configuration file shown in Figure 5-7.

- Page 77 Project Generation When users press the Generate button, the DE2-115 System Builder will generate the corresponding Quartus II files and documents as listed in the Table 5-1: Table 5-1 The files generated by DE2-115 System Builder Filename Description <Project name>.v Top level verilog HDL file for Quartus II <Project name>.qpf...

Page 78: Chapter 6 Examples Of Advanced Demonstrations

Page 79: tv box demonstration.

- Page 80 4:3 aspect ratio o Non-progressive video Connect the VGA output of the DE2-115 board to a VGA monitor (both LCD and CRT type of monitors should work) Connect the audio output of the DVD player to the line-in port of the DE2-115 board and connect a speaker to the line-out port.

Page 81: Usb Paintbrush

- Page 82 Nios II Workspace: DE2_115_NIOS_HOST_MOUSE_VGA\Software Connect a USB Mouse to the USB Host Connector (type A) of the DE2-115 board Connect the VGA output of the DE2-115 board to a VGA monitor (both LCD and CRT type of monitors should work) ...

Page 83: Usb Device

- Page 84 Bit stream used: DE2_115_NIOS_DEVICE_LED.sof Nios II Workspace: DE2_115_NIOS_DEVICE_LED\Software Borland C++ Software Driver: DE2_115_NIOS_DEVICE_LED\SW Connect the USB Device connector of the DE2-115 board to the host computer using a USB cable (type AB). Load the bit stream into FPGA(note*) ...

Page 85: A Karaoke Machine

- Page 86 Project directory: DE2_115_i2sound Bit stream used: DE2_115_i2sound.sof or DE2_115_i2sound.pof Connect a microphone to the microphone-in port (pink color) on the DE2-115 board Connect the audio output of a music-player, such as an MP3 player or computer, to the line-in port (blue color) on the DE2-115 board ...

Page 87: Sd Card Demonstration

- Page 88 LED if it fails to parse the FAT file system or if there is no SD Card found in the SD Card socket of the DE2-115 board. If users press KEY3 of the DE2-115 board,...

- Page 89 Make sure Quartus II and Nios II are installed on your PC. Power on the DE2-115 board. Connect USB Blaster to the DE2-115 board and install USB Blaster driver if necessary. Execute the demo batch file “DE2_115_SD_Card.bat” under the batch file folder, DE2_115_SD_CARD\demo_batch.

Page 90: Sd Card Music Player

- Page 91 Figure 6-13 shows the hardware block diagram of this demonstration. The system requires a 50 MHz clock provided from the board. The PLL generates a 100MHz clock for Nios II processor and the other controllers except for the audio controller. The audio chip is controlled by the Audio Controller which is a user-defined SOPC component.

- Page 92 7-segment display, and the LEDs. The top and bottom row of the LCD module will display the file name of the music that is played on the DE2-115 board and the value of music volume, respectively. The 7-segment displays will show the elapsed time of the playing music file. The LED will indicate the audio signal strength.

- Page 93 Connect a headset or speaker to the DE2-115 board and you should be able to hear the music played from the SD Card Press KEY3 on the DE2-115 board to play the next music file stored in the SD Card.

Page 94: Ps/2 Mouse Demonstration

- Page 95 Data transmit from the device to controller After sending an enabling instruction to the PS/2 mouse at stream mode, the device starts to send displacement data out, which consists of 33 bits. The frame data is cut into three similar slices, each of them containing a start bit (always zero) and eight data bits (with LSB first), one parity check bit (odd check), and one stop bit (always one).

- Page 96 Figure 6-16 Waveforms on two lines while communication taking place Demonstration Setup, File Locations, and Instructions Project directory: DE2_115_PS2_DEMO Bit stream used : DE2_115_PS2_DEMO.sof Load the bit stream into FPGA by executing DE2_115_PS2_DEMO\demo_batch\DE2_115_PS2_DEMO.bat Plug in the PS/2 mouse ...

Page 97: Ir Receiver Demonstration

- Page 98 Figure 6-18 Remote controller Table 6-3 Key code information for each Key on remote controller Key Code Key Code Key Code Key Code 0x0F 0x13 0x10 0x12 0x01 0x02 0x03 0x1A 0x04 0x05 0x06 0x1E 0x07 0x08 0x09 0x1B 0x11 0x00 0x17 0x1F...

- Page 99 After the IR receiver on DE2-115 board receives this frame, it will directly transmit that to FPGA. In this demo, the IP of IR receiver controller is implemented in the FPGA. As Figure 6-20 shows, it includes Code Detector, State Machine, and Shift Register. First, the IR receiver demodulates the signal inputs to Code Detector block .The Code Detector block will check the Lead Code and...

- Page 100 We can apply the IR receiver to many applications, such as integrating to the SD Card Demo, and you can also develop other related interesting applications with it. Demonstration Setup, File Locations, and Instructions Project directory: DE2_115_IR Bit stream used: DE2_115_IR.sof ...

Page 101: Music Synthesizer Demonstration

- Page 102 Bit stream used: DE2_115_Synthesizer.sof or DE2-115_Synthesizer.pof Connect a PS/2 Keyboard to the DE2-115 board. Connect the VGA output of the DE2-115 board to a VGA monitor (both LCD and CRT type of monitors should work) Connect the lineout of the DE2-115 board to a speaker.

- Page 103 Table 6-5 Table 6-6 illustrate the usage of the slide switches, push-button switches (KEYs), PS/2 Keyboard. Slide Switches and Push-buttons switches Table 6-5 Usage of the slide switches and push-buttons switches (KEYs) Signal Name Description KEY[0] Reset Circuit KEY[1] Repeat the Demo Music SW[0] OFF: BRASS, ON: STRING...

Page 104: Audio Recording And Playing

- Page 105 Figure 6-25 Man-Machine Interface of Audio Recorder and Player Figure 6-26 shows the block diagram of the Audio Recorder and Player design. There are hardware and software parts in the block diagram. The software part stores the Nios II program in SRAM. The software part is built by Nios II IDE in C programming language.

- Page 106 Bit stream used: DE2_115_AUDIO.sof Software Project directory: DE2_115_AUDIO\software\ Connect an Audio Source to the LINE-IN port of the DE2-115 board. Connect a Microphone to MIC-IN port on the DE2-115 board. Connect a speaker or headset to LINE-OUT port on the DE2-115 board.

Page 107: Web Server Demonstration

- Page 108 Figure 6-27 MII interface MAC Configuration...

- Page 109 Figure 6-28 RGMII interface MAC Configuration In the MAC Options tab (See Figure 6-29), users should set up proper values for the PHY chip 88E1111. The MDIO Module should be included, as it is used to generate a 2.5MHz MDC clock for the PHY chip from the controller's source clock(here a 100MHz clock source is expected) to divide the MAC control register interface clock to produce the MDC clock output on the MDIO interface.

- Page 110 Figure 6-29 MAC Options Configuration Once the Triple-Speed Ethernet IP configuration has been set and necessary hardware connections have been made as shown in Figure 6-30, click on generate.

- Page 111 Figure 6-30 SOPC Builder Figure 6-31 shows the connections for programmable 10/100Mbps Ethernet operation via MII. Figure 6-31 PHY connected to the MAC via MII Figure 6-32 shows the connections for programmable 10/100/1000Mbps Ethernet operation via RGMII.

- Page 112 Figure 6-33. The top block contains the Nios II processor and the necessary hardware to be implemented into the DE2-115 host board. The software device drivers contain the necessary device drivers needed for the Ethernet and other hardware components to work.

- Page 113 NicheStack™ TCP/IP Stack will start to run for Web Server application. Figure 6-34 describes this demo setup and connections on DE2-115. The Nios II processor is running NicheStack™ on the MicroC/OS-II RTOS. Note: your gateway should support DHCP because it uses DHCP protocol to request a valid IP from the Gateway, or else you would need to reconfigure the system library to use static IP assignment.

- Page 114 You will see the brand new DE2-115 webpage on your computer On the web page, you could access the DE2-115 board‟s peripherals from the left sidebar or link to external pages from the right sidebar. Try check some LEDs on the left sidebar and then press send will light up the specified LEDs on board.

- Page 115 Note: Or execute DE2_115_Web_Server\<Web Server Mode-Port Specific>\demo_batch\web_server.bat for downloading .sof and .elf files. Figure 6-34 System Principle Diagram Figure 6-35 Served web page for DE2-115...

Page 116: Chapter 7 Appendix

Rename the bookmark, delete bookmark, delete from my manuals, upload manual.

Success! Subscription added.

Success! Subscription removed.

Sorry, you must verify to complete this action. Please click the verification link in your email. You may re-send via your profile .

- Intel Community

- Product Support Forums

- FPGA, SoC, And CPLD Boards And Kits

Need a pin assignments for kit FPGA Cyclone IV EP4CE6E22C8N

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Printer Friendly Page

- Mark as New

- Report Inappropriate Content

- All forum topics

- Previous topic

Link Copied

Community support is provided during standard business hours (Monday to Friday 7AM - 5PM PST). Other contact methods are available here .

Intel does not verify all solutions, including but not limited to any file transfers that may appear in this community. Accordingly, Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

For more complete information about compiler optimizations, see our Optimization Notice .

- ©Intel Corporation

- Terms of Use

- *Trademarks

- Supply Chain Transparency

- Search forums

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

Welcome to EDAboard.com

Welcome to our site edaboard.com is an international electronics discussion forum focused on eda software, circuits, schematics, books, theory, papers, asic, pld, 8051, dsp, network, rf, analog design, pcb, service manuals... and a whole lot more to participate you need to register. registration is free. click here to register now..

- Digital Design and Embedded Programming

- PLD, SPLD, GAL, CPLD, FPGA Design

[SOLVED] pin assignments for altera cyclone iii fpga kit

- Thread starter preethi19

- Start date Mar 23, 2016

- Mar 23, 2016

Full Member level 5

Trickydicky, advanced member level 7.

Which board is it? that part number is just the FPGA part number. The board documentation will tell you the pinout, not the FPGA.

Super Moderator

Guess you are talking about the Altera 3C25 starter board? A convenient way to import the pin assignments is to copy it from a demo project provided with the development kit. It's in the *.qsf file, the TCL statements assigning the pins can be entered in the Quartus TCL console. If you want to do it from the scratch, review the schematics in the "board design file" folder, specify the pin assignments in the pin planner tool.

Similar threads

- Started by hexaeder

- Mar 18, 2024

- Started by MLSD

- Aug 23, 2023

- Started by rllv24

- Mar 24, 2024

- Started by dpaul

- Feb 23, 2024

- Started by engr_joni_ee

- Apr 3, 2024

Part and Inventory Search

Welcome to edaboard.com.

- This site uses cookies to help personalise content, tailor your experience and to keep you logged in if you register. By continuing to use this site, you are consenting to our use of cookies. Accept Learn more…

Solving FPGA I/O pin assignment challenges

Editor's Note: I've long been impressed by Xcell Journal from Xilinx, both for the quality of its production and the quality of its articles.

A few weeks ago we looked at an article on

Replacing obsolete video game circuits with Xilinx CPLDs , and now I'm delighted to have the opportunity to present the following piece from the Third Quarter 2008 issue of Xcell Journal, with the kind permission of Xilinx.

Input/Output (I/O) pin assignment is one of the main challenges facing designers integrating large FPGA devices onto PCBs. Many designers find the process of defining the I/O pin configuration, or “pinout,” of large FPGA devices and their advanced BGA packages an increasingly difficult task for a seemingly ever-expanding number of reasons. But with a mix of smart I/O planning and new tools, you can remove the pain from the pinout process.

The task of defining an I/O pinout from FPGA to PCB is a major design challenge that can make or break a design. You must balance requirements from both the FPGA and PCB perspectives while designing both sides in parallel. If you prematurely optimize a pinout specifically for the PCB or the FPGA, it can lead to design issues in the other domain.

In order to understand the ramifications of your pin assignment choices, you need to be able to visualize both the PCB placement and FPGA physical device pins, along with the internal FPGA I/O pads and related resources. Unfortunately, as of today, there isn't just one tool or methodology to address all of these co-design concerns.

What you can do, however, is combine various techniques and strategies to optimize the pin-planning process and add new co-design tools like Xilinx PinAhead technology to devise an effective pinout methodology (Xilinx includes PinAhead in its ISE software design suite 10.1).

At Xilinx, we have developed a rule-driven methodology in which we define an initial pinout that considers both the PCB and FPGA requirements, allowing each design group to begin their respective design processes as early as possible by using a pinout that should be very close to the finalized version. If the design requires changes because of PCB routability or internal FPGA performance issues late in the process, this methodology is such that those issues are typically localized, requiring you to make only small changes in either design domain.

Step 1: Evaluating the Design Parameters So where should you start? You should begin to formulate an I/O strategy as early as possible. But you may find this task difficult in the absence of an optimal tool for the job or a complete netlist.

First, let's examine the PCB physical parameters and limitations by answering a few questions:

- What is the preferred layer count, trace width, and via size?

- Do the PCB parameters limit the FPGA package types that you can use, such as BGA?

- Are there any fixed interface locations for the FPGA on the PCB? Other chips, connecters, or placement restrictions?

- Which high-speed interfaces need special attention?

- Can you visualize a placement strategy to enable the shortest interconnect?

You may find it helpful to draw a diagram of the proposed PCB placement â including all major components with critical interfaces and buses â so as to determine the best FPGA pin assignment locations. Make sure that you draw the components on the side of the board where you plan to mount those components. Make note of interfaces that will require special attention, such as high-speed buses and differential pairs as illustrated in Fig 1 .

Next, examine the layout of the FPGA device to understand where the physical resources exist on the silicon. List the various voltages and clocks you are using in the design to begin to isolate the interfaces the design will require. Then determine if your design uses specific I/O interface resources such as giga transceivers (GTs), BUFRs, IODELAY, and digital clock managers that require you to define and route I/O pins in close proximity to each other.

Now it's time to locate the FPGA resources, such as PowerPCs, DSP48s, and RAM16s, in the design. It makes sense for you to target any related I/Os to the I/O banks closest to those resources. See if you can group any of the I/O signals into interfaces; this will help during pin assignment. Finally, determine the configuration mode for the FPGA.

Step 2: Defining Pinout Requirements Once you understand the main FPGA interfaces and have created a mockup of the physical layout, you can start to define the pinout. Some designers like to use a spreadsheet containing all of the I/O signals to keep track of the pins. You can group them by voltage, by clocks, by interface, or by bus. This method is really quite valuable because it helps you begin to formulate the groups of signals you will assign in close proximity. At this stage, you should also identify critical interfaces that must exit the device on a particular edge or use outside physical pins for optimal PCB routing.

After examining both the FPGA and PCB requirements and defining the major interface locations, the next step is to begin assigning pins to I/O banks based on all of the preceding criteria. This is where the real work begins. In the current flow, pin assignment is a time-consuming task that can involve a lot of trial and error to solve any performance and signal integrity concerns. Designers have traditionally performed this task freehand, because EDA and chip vendors didn't offer tools to effectively help designers visualize the two domains.

But now, Xilinx has a tool for the job. PlanAhead Lite, which we've included in the 10.1 release of the ISE Foundation software toolset, is a subset of the PlanAhead software design, analysis, and floorplanning tool. It includes a tool called PinAhead, which addresses both PCB and FPGA design concerns and makes I/O pinout configuration much easier for designers.

Rather than go into detail about every feature of the tool, let's see how we can use it in the context of an I/O pin assignment methodology (if you want more detailed information about PinAhead, including a video demonstration and tutorial, visit www.xilinx.com/planahead ).

Step 3: Using PinAhead for Assigning the Pinout The PinAhead environment displays a set of views applicable to the task of exploring and assigning I/O port signals to physical package pins or I/O pads on the die as illustrated in Fig 2 .

PinAhead has virtually the same graphical environment as PlanAhead software, clearly displaying the silicon I/O pads and related resources in the “Device” view and the physical device pins in the “Package” view. The views present both I/O port and physical pin information so that you can cross-select to explore the logical design and physical device resources.

You can use PinAhead in the absence of a design netlist to explore device resources or to start the I/O pin planning process. The “Package Pins” view lists device package specifications according to the device data sheets, so in most cases you won't have to cross-reference the device data sheet when configuring the pinout. The Package Pins view table categorizes I/O banks, allowing you to cross-select and highlight I/O banks in both the Device and Package views. The view clearly shows the relationship between the physical pin location and the I/O pad location on the die, which simplifies optimal I/O bank selection. The Package Pins' “Pin” view also displays information for each pin in the I/O bank.

You can begin creating I/O ports from scratch using the PinAhead interface or by importing them from a comma separated value (CSV) format spreadsheet, HDL source file headers, or a synthesized netlist and UCF format constraints file. The “I/O Ports” view displays all of the I/O port signals you have currently defined in the design, and the bus folders display the grouped buses and differential pair signals.

You can sort the Package Pins and I/O Ports views in a variety of ways. You can toggle the list views to display a category-based list or a flat list, and with just a mouse click, sort the Package Pins view to display all available global clock- or regional clock-capable pins. You can also export the information to a CSV format spreadsheet to use as a starting point for pinout configuration.

PinAhead also has an interface to allow you to selectively prohibit I/O pins, groups of I/O pins, or I/O banks from having I/O ports assigned to them by PinAhead. You can select and prohibit pins in the Package Pins, Device or Package views. For example, you can sort the Package Pins view and prohibit all VREF pins.

PinAhead allows you to group related I/O ports and buses into an “interface.” This grouping simplifies I/O port management and assignment tasks by allowing you to handle related I/O ports as a single entity. The interface grouping makes it much easier for you to visualize and manage all of the signals associated with a particular logic interface.

You can easily copy interfaces from design to design or use them to generate interface-specific PCB schematic symbols. The interfaces appear as expandable folders in the I/O Ports view, and you can add additional I/O ports to the interface by selecting them in that view and dragging them into the interface folder.

As you create the I/O ports, you can assign them to package pins or I/O pads. Before you do this, it pays to examine the I/O ports' initial PCB interconnect sketch and consult with the PCB designer to understand the desired locations and other considerations for placing the various I/O port interfaces. Proper bus order and edge proximity can aid PCB routing significantly and save design time.

You can assign individual pins, buses, and interfaces to I/O pins by dragging them into either the Device or Package views. You can assign the entire group of pins to the selected I/O pins using various assignment pattern modes. The available modes include “Place I/O Ports in an I/O Bank,” “Place I/O Ports in Area,” and “Place I/O Ports Sequentially.”

Each mode offers a different assignment pattern for the I/O ports you are assigning to pins. Using these modes, you will see information about the number of ports you are placing by looking at the pop-up window on your mouse cursor's tip. This mode remains active until you have placed all of the selected I/O ports.

PlanAhead software attempts to maintain your correct-by-assignment rules. With your guidance, the tool will assign differential pair ports into proper pin pairs. As you interactively assign I/O ports with the tool, the tool runs design rule checking (DRC) to ensure legal placement.

The tool's default setting runs in interactive DRC mode, but you can toggle it off if you choose. The tool checks for conflicting voltages, VREF pins, or I/O standards, as well as noise-sensitive pins located near GT devices. When it finds an error, the tool displays a Tooltip indicating why you can't assign an I/O port to a specific pin.

You can activate PinAhead's “Autoplace” command to direct the tool to automatically place all or any selected I/O ports to package pins. The Autoplace command will obey all I/O standard and differential pair rules and will place global clock pins appropriately. The command will also attempt to group interfaces as much as possible.

The Device view graphically displays all clock regions and clock-related logic objects, making I/O assignment based on clocks much easier and intuitive. Selecting a clock region will display all of the I/O banks, clock-related resources, and device resources associated with it. This makes the process of regional clock planning much easier by allowing exploration of the available resources along with their physical relationship.

You can also use PinAhead to place other I/O related logic in your design, such as BUFGs, BUFRs, IODELAYs, IDELAYCTRLs, and DCMs. You can easily locate these objects and placement sites in PlanAhead by using the “Find” command. To selectively explore and expand logic and logic connectivity, use the tool's “Schematic” view.

You can also lock the placement of specific I/O-related logic with PlanAhead software by selecting the logic in any view and dragging it onto sites in the Device view.

PlanAhead software will only allow you to place logic on appropriate sites. A dynamic cursor identifies the proper site locations as you are dragging a logic object over the design.

Step 4: Running DRC and WASSO for Legal Sign-Off Once you've completed your pin assignment, you can use PinAhead's vast set of DRC rules to run a sign-off DRC and ensure that the design is error-free before running the PlanAhead software implementation tools. The tool has many I/O and clock-related rules to ensure that I/O placement is legal. You can select rules using the PlanAhead software DRC dialog.

If the tool finds rule violations, it displays a DRC results table with the errors. You can select the errors to investigate them further.

PlanAhead software also includes weighted average simultaneous switching output (WASSO) analysis to help you identify potential signal integrity issues with the pinout configurations. You feed the tool the parasitic characteristics of your PCB design; PlanAhead software will analyze the various I/O banks and their neighbors and report back the utilization and status of each I/O bank.

Step 5: Exporting the I/O Pinout You can export the I/O port list and package pin information from PlanAhead software into a CSV format file, HDL header, or UCF file. The CSV file includes information about all of the package pins in the device, as well as design-specific I/O port assignments and their configurations. The package pin section of the list makes a great starting point for defining I/O port definitions in the spreadsheet.

You can also use the spreadsheet to automatically generate the PCB schematic symbols your group needs to begin the PCB layout. Sometimes, however, these symbols are too large for the schematic; you'll have to break them up into several symbols. You can do this quite effectively using the interface groups created in PinAhead.

Providing this I/O pinout configuration in the form of a schematic symbol gives PCB designers a good foundation to start developing an effective PCB layout. Because you developed the initial pinout with the PCB interfaces in mind, it should be fairly close to the final pinout configuration.

And if you do need to swap pins during layout to facilitate routing, you should be able to make those changes easily, because â more likely than not â the pins that require swapping are conveniently located within the I/O banks. And the methodology shouldn't affect the FPGA design too drastically. You can transfer revised pinout spreadsheets or UCF files between your PCB and FPGA designers to keep in sync with any modifications you've made.

You may also wish to tie the unused pins or certain configuration pins to either VCC or GND (ground) to help with signal noise concerns and facilitate proper FPGA functionality. At Xilinx, we are currently working on a function for the next version of PinAhead that will provide an interface for FPGA designers to specify these pins and include the pins' connections in the output CSV spreadsheet. This will allow PCB designers to more easily identify pins and connect them appropriately.

Moving forward, as FPGAs employ more complex functions and use more advanced packages, devising a solid FPGA and PCB pinout methodology will become imperative. Although we think you'll find PinAhead Lite a great help in executing your co-design-savvy pinout strategies today, we are already working on improvements to the tool to better help you tackle pinout challenges and get the job done.

Brian Jackson is a Product Marketing Manager at Xilinx ; he can be contacted at .

Share this:

Leave a reply cancel reply.

You must Register or Login to post a comment.

This site uses Akismet to reduce spam. Learn how your comment data is processed .

COMMENTS

Functional Pin Information. Intel provides device pin-out information in three formats: PDF, XLS, and TXT. Find files for Agilex Devices, Stratix Devices, Arria Devices, Cyclone Devices, MAX Devices, and more.

1. Use the Intel® Quartus® Prime Pin Planner to make pin assignments. 2. Use Intel® Quartus® Prime Fitter messages and reports for sign-off of pin assignments. 3. Verify that the Intel® Quartus® Prime pin assignments match those in the schematic and board layout tools. With the Intel® Quartus® Prime Pin Planner GUI, you can identify I/O ...

DE2-115 Board I/O Pin Assignments: Switches, LEDs, and 7-Segment Displays. Table 1: Pin assignments for slide switches. Table 2: Pin assignments for pushbutton (debounced) switches. Table 3: Pin assignments for LEDs. Table 4: Pin assignments for 7-segment displays. Table 5: Pin assignments for clock inputs.

I haven't worked with Altera, but in Xilinx you could manually specify pin assignments before the compile in the constraints file (.UCF for Xilinx). From what I can tell, you can do the same thing for Altera in the Quartus II .QSF file by using set_location_assignment. See the example .QSF file on page 6 in this Quartus II Handbook.

This is a tutorial on how to assign the Input & Output of your HDL code to an Intel Altera Cyclone II FPGA pins using Intel Altera Qaurtus II version 13 usin...

3. Pin Assignment The DE2 board has hardwired connections between the FPGA pins and the other components on the board. For this project, we need to access LED, LCD. 7-Segment LEDs and serial port. The wrapper file already mapped the input and output pins to their default names as used by alter pin assignment file. To import pin assignment file ...

connected to the FPGA pins N25, N26 and P25, respectively. We will connect the output sum and cout to the green light-emitting diodes labeled LEDG0 and LEDG1, which is hardwired to the FPGA pin AE22 and AF22. Pin assignments are made by using the Assignment Editor. Select Assignments > Assignment Editor to reach the window in Figure 13. Enter ...

PLLs on altera FPGAs usually have dedicated input pins. From the pin assignment, it works out which PLL to place into, rather than the other way round. Regardless, the clock pins will already be connected on the PCB, so you have to assign it mannually anyway (regardless of whether its Xilinx or Altera). 0 Kudos.

32. Choose Assignments → Pins, which opens the Pin Planner, a spreadsheet-like table of specific pin assignments. The Pin Planner shows the design's pins. 33. In the Location column next to each of the node names, add the coordinates (pin numbers) for the actual values to use with the board. For the pin layout of components on

numbers) for the actual values to use with the board. (For the pin layout of components on the Board, please refer to Appendix A.) For the Counter example used in this tutorial, please refer to below pin assignment Table 1. Signal Name FPGA Pin Signal Name FPGA Pin Clock PIN_L1 digit[6] PIN_J2 Reset PIN_R22 digit[5] PIN_J1 Q[0] PIN_ R20 digit[4 ...

LCD_RS PIN_K1 LCD Command/Data Select, 0 = Command, 1 = Data LCD_ON PIN_L4 LCD Power ON/OFF LCD_BLON PIN_K2 LCD Back Light ON/OFF Signal Name FPGA Pin No. Description SD_DAT PIN_AD24 SD Card Data SD_DAT3 PIN_AC23 SD Card Data 3 SD_CMD PIN_Y21 SD Card Command Signal SD_CLK PIN_AD25 SD Card Clock Signal Name FPGA Pin No. Description

View and Download Altera DE2-115 user manual online. DE2-115 computer hardware pdf manual download. ... Page 43 Figure 4-14 LVDS interface on HSMC connector and Cyclone IV E FPGA Table 4-9 Pin Assignments for HSMC connector FPGA Pin Signal Name Description I/O Standard HSMC_CLKIN0 PIN_AH15 Depending Dedicated clock input on JP6 HSMC_CLKIN_N1 ...

Dear Altera, My name is Phu Nguyen. I am looking for a file pin assignment for kit FPGA Cyclone IV EP4CE6E22C8N. I used to use kit DE2 and have a file exel DE2_pin_assignment but i can't find a file for kit FPGA Cyclone IV EP4CE6E22C8N. Can you give me or link of file pin assignment for kit FPGA Cyclone IV EP4CE6E22C8N.

Hello, Altera's Quartus has 3 ways to assign pins to the FPGA device: 1. Assignment Editor. 2. Pin Planner. 3. Direct text input into *.QSF. My question: Are these tools synchronized with each other? For example: if I do initial assignments using the Pin Planner and then make changes in...

A convenient way to import the pin assignments is to copy it from a demo project provided with the development kit. It's in the *.qsf file, the TCL statements assigning the pins can be entered in the Quartus TCL console. If you want to do it from the scratch, review the schematics in the "board design file" folder, specify the pin assignments ...

number of nets in the subsymbol and the length of the longest net name, and annotated with the pin assignments for each net. It's still not as great as the FPGA integration in some of the commercial Schematic/Layout packages, but it's a huge improvement over trying to manually create symbols for your FPGA (mine has 672 pins!)

Intel® MAX® 10 FPGA Pin Connection Guidelines Power Supply Sharing Guidelines for Intel® MAX® 10 FPGA Devices Document Revision History for Intel® MAX® 10 FPGA Device Family Pin Connection Guidelines. Intel® MAX® 10 FPGA Pin Connection Guidelines x. Clock and PLL Pins Configuration/JTAG Pins Differential I/O Pins External Memory ...

Input/Output (I/O) pin assignment is one of the main challenges facing designers integrating large FPGA devices onto PCBs. Many designers find the process of defining the I/O pin configuration, or "pinout," of large FPGA devices and their advanced BGA packages an increasingly difficult task for a seemingly ever-expanding number of reasons.

Pin Information for the Cyclone® IV EP4CE6 Device Version 1.2. This is a top view of the silicon die. This is only a pictorial representation to provide an idea of placement on the device. For exact locations, refer to the pin list and the Quartus® II software. Initial Release.