Blocking vs. Nonblocking in Verilog

The concept of Blocking vs. Nonblocking signal assignments is a unique one to hardware description languages. The main reason to use either Blocking or Nonblocking assignments is to generate either combinational or sequential logic. In software, all assignments work one at a time. So for example in the C code below:

The second line is only allowed to be executed once the first line is complete. Although you probably didn’t know it, this is an example of a blocking assignment. One assignment blocks the next from executing until it is done. In a hardware description language such as Verilog there is logic that can execute concurrently or at the same time as opposed to one-line-at-a-time and there needs to be a way to tell which logic is which.

<= Nonblocking Assignment

= Blocking Assignment

The always block in the Verilog code above uses the Nonblocking Assignment, which means that it will take 3 clock cycles for the value 1 to propagate from r_Test_1 to r_Test_3. Now consider this code:

See the difference? In the always block above, the Blocking Assignment is used. In this example, the value 1 will immediately propagate to r_Test_3 . The Blocking assignment immediately takes the value in the right-hand-side and assigns it to the left hand side. Here’s a good rule of thumb for Verilog:

In Verilog, if you want to create sequential logic use a clocked always block with Nonblocking assignments. If you want to create combinational logic use an always block with Blocking assignments. Try not to mix the two in the same always block.

Nonblocking and Blocking Assignments can be mixed in the same always block. However you must be careful when doing this! It’s actually up to the synthesis tools to determine whether a blocking assignment within a clocked always block will infer a Flip-Flop or not. If it is possible that the signal will be read before being assigned, the tools will infer sequential logic. If not, then the tools will generate combinational logic. For this reason it’s best just to separate your combinational and sequential code as much as possible.

One last point: you should also understand the semantics of Verilog. When talking about Blocking and Nonblocking Assignments we are referring to Assignments that are exclusively used in Procedures (always, initial, task, function). You are only allowed to assign the reg data type in procedures. This is different from a Continuous Assignment . Continuous Assignments are everything that’s not a Procedure, and only allow for updating the wire data type.

Leave A Comment Cancel reply

Save my name, email, and website in this browser for the next time I comment.

Blocking and Non-blocking Assignment in Verilog

- Assignment is only done in procedural block(always ot initial block)

- Both combintational and sequential circuit can be described.

- Assignment can only possible to reg type irrespect of circuit type

Let's say we want to describe a 4-bit shift register in Verilog. For this, we are required to declare a 3-bit reg type variable.

The output of shift[0] is the input of shift[1], output of shift[1] is input of shift[2], and all have the same clock. Let's complete the description using both assignment operator.

Non-Blocking Assignment

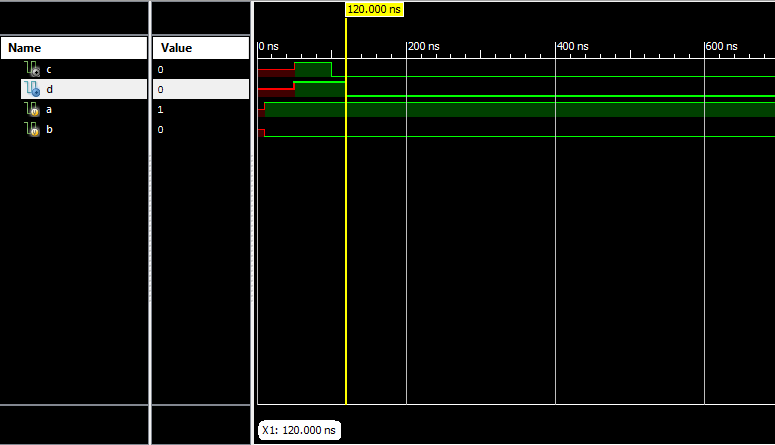

When we do synthesis, it consider non-blocking assignment separately for generating a netlist. If we see register assignment in below Verilog code, all register are different if we consider non-blocking assignment separately. If you do the synthesis, it will generate 3 registers with three input/output interconnects with a positive edge clock interconnect for all register. Based on the Verilog description, all are connected sequentially because shift[0] is assigned d, shift[1] is assigned shift[0], and shift[2] is assigned shift[1].

Blocking Assignment

If we use blocking assignment and do the syhtheis, the synthesis tool first generate netlist for first blocking assignment and then go for the next blocking assignment. If in next blocking assignment, if previous output of the register is assigned to next, it will generate only a wire of previously assigned register.

In below Verilog code, even though all looks three different assignment but synthesis tool generate netlist for first blocking assigment which is one register, working on positive edge of clock, input d and output shift[0]. Since blocking assignment is used, for next blocking assignment, only wire is generated which is connected to shift[0]. Same is for next statement a wire is generated which is connected to shift[0].

Click like if you found this useful

Add Comment

This policy contains information about your privacy. By posting, you are declaring that you understand this policy:

- Your name, rating, website address, town, country, state and comment will be publicly displayed if entered.

- Your IP address (not displayed)

- The time/date of your submission (displayed)

- Administrative purposes, should a need to contact you arise.

- To inform you of new comments, should you subscribe to receive notifications.

- A cookie may be set on your computer. This is used to remember your inputs. It will expire by itself.

This policy is subject to change at any time and without notice.

These terms and conditions contain rules about posting comments. By submitting a comment, you are declaring that you agree with these rules:

- Although the administrator will attempt to moderate comments, it is impossible for every comment to have been moderated at any given time.

- You acknowledge that all comments express the views and opinions of the original author and not those of the administrator.

- You agree not to post any material which is knowingly false, obscene, hateful, threatening, harassing or invasive of a person's privacy.

- The administrator has the right to edit, move or remove any comment for any reason and without notice.

Failure to comply with these rules may result in being banned from submitting further comments.

These terms and conditions are subject to change at any time and without notice.

Comments (1)

hey in blocking assignment do we get shift in data i dont think so . we get all values same and equal to d.

Please do not focus on the module name; focus on how the netlist is generated after the synthesis.

Blocking (immediate) and Non-Blocking (deferred) Assignments in Verilog

There are Two types of Procedural Assignments in Verilog.

- Blocking Assignments

- Nonblocking Assignments

To learn more about Delay: Read Delay in Assignment (#) in Verilog

Blocking assignments

- Blocking assignments (=) are done sequentially in the order the statements are written.

- A second assignment is not started until the preceding one is complete. i.e, it blocks all the further execution before it itself gets executed.

Non-Blocking assignments

- Nonblocking assignments (<=), which follow each other in the code, are started in parallel.

- The right hand side of nonblocking assignments is evaluated starting from the completion of the last blocking assignment or if none, the start of the procedure.

- The transfer to the left hand side is made according to the delays. An intra- assignment delay in a non-blocking statement will not delay the start of any subsequent statement blocking or non-blocking. However normal delays are cumulative and will delay the output.

- Non-blocking schedules the value to be assigned to the variables but the assignment does not take place immediately. First the rest of the block is executed and the assignment is last operation that happens for that instant of time.

To learn more about Blocking and Non_Blocking Assignments: Read Synthesis and Functioning of Blocking and Non-Blocking Assignments

The following example shows interactions between blocking and non-blocking for simulation only (not for synthesis).

For Synthesis (Points to Remember):

- One must not mix “<=” or “=” in the same procedure.

- “<=” best mimics what physical flip-flops do; use it for “always @ (posedge clk..) type procedures.

- “=” best corresponds to what c/c++ code would do; use it for combinational procedures.

Spread the Word

- Click to share on Facebook (Opens in new window)

- Click to share on Twitter (Opens in new window)

- Click to share on LinkedIn (Opens in new window)

- Click to share on Pinterest (Opens in new window)

- Click to share on Tumblr (Opens in new window)

- Click to share on Pocket (Opens in new window)

- Click to share on Reddit (Opens in new window)

- Click to email a link to a friend (Opens in new window)

- Click to print (Opens in new window)

Related posts:

- Synthesis and Functioning of Blocking and Non-Blocking Assignments.

- Delay in Assignment (#) in Verilog

- Ports in Verilog Module

- Module Instantiation in Verilog

Post navigation

Leave a reply cancel reply.

Your email address will not be published. Required fields are marked *

Save my name, email, and website in this browser for the next time I comment.

Notify me of follow-up comments by email.

Notify me of new posts by email.

Procedural Assignments

In the dataflow modeling, a continuous assignment statement is discussed where LHS expression is always updated for changes in RHS expression. Refer to c ontinuous assignment for more details. In the case of procedural assignment, the LHS variable remains unchanged until the same value is updated by the next procedural statement.

- RHS expression can be a value or an expression that evaluates to a value.

- LHS expression can be reg, integer, real, time-variable, or memory element.

- The procedural assignments can be placed inside procedural blocks like initial and always blocks. They can also be placed inside tasks and functions.

- The procedural assignments can also be placed directly inside a module while declaring a variable. (Ex. reg [3:0] i_data = 4’h7)

There are two types of procedural assignments and both of them are widely used in the designs written in the Verilog language.

- Blocking assignments

- Non-blocking assignments

Blocking Assignments

The blocking assignment statements are executed sequentially by evaluating the RHS operand and finishes the assignment to LHS operand without any interruption from another Verilog statement. Hence, it blocks other assignments until the current assignment completes and is named as “blocking assignment”.

An equal ‘=’ is used as a symbol for the blocking assignment operator.

A blocking assignment does not block the execution of a statement in another procedural block. For example, two initial blocks start execution at the same simulation time. A blocking assignment in the first initial block does not block execution in another initial block.

Race around condition: A problem with blocking assignment

If a variable is used in LHS of blocking assignment in one procedural block and the same variable is used in RHS of another blocking assignment in another procedural block. The race-around condition can occur as an order of execution is unknown if both statements are scheduled at the same simulation time.

In this example,

Since procedural blocks (both initial and always) can be executed in any order.

A. If the first initial block executed before the second initial block then

- The value of y will be updated as 4‘h5 in the first initial block

- The value of data will be updated as 4‘h5 in the second initial block

B. If the second initial block executed before the first initial block then

- The value of data will be updated as 4‘h3 in the second initial block

- The value of y will be updated as 4‘h3 in the first initial block

Verilog Tutorials

Verification Guide

SystemVerilog Blocking assignment

Blocking assignment.

Blocking assignment statements execute in series order. Blocking assignment blocks the execution of the next statement until the completion of the current assignment execution.

Blocking assignment example

In Below Example, a and b is initialized with value 10 and 15 respectively, after that b is being assigned to a (a value will become 15), and value 20 is assigned to b. After assignment value of a = 15 and b=20.

Simulator Output:

Blocking assignment example-2

In Below Example, a and b are initialized with value 10 and 15 respectively, after that b is being assigned to a (a value will become 15), and value 20 is assigned to b. After assignment value of a = 15 and b = 20.

❮ Previous Next ❯

- Interview Q

Verilog Tutorial

- Send your Feedback to [email protected]

Help Others, Please Share

Learn Latest Tutorials

Transact-SQL

Reinforcement Learning

R Programming

React Native

Python Design Patterns

Python Pillow

Python Turtle

Preparation

Verbal Ability

Interview Questions

Company Questions

Trending Technologies

Artificial Intelligence

Cloud Computing

Data Science

Machine Learning

B.Tech / MCA

Data Structures

Operating System

Computer Network

Compiler Design

Computer Organization

Discrete Mathematics

Ethical Hacking

Computer Graphics

Software Engineering

Web Technology

Cyber Security

C Programming

Control System

Data Mining

Data Warehouse

Verilog Blocking & Non-Blocking assignments elaborated

- Post author By Kevin

- Post date 20 October 2020

Blocking / Non-Blocking assignment rules

The main reason to use either Blocking or Non-Blocking assignments is to generate either combinational or sequential logic.

In non-blocking assignments (<=), all registers inside the always block are updated at the end. In blocking assignments (=), the registers are updated immediately.

Whether or not a flip-flop is inferred from a blocking assignment depends on whether or not the value of the variable being assigned needs to be remembered from one clock edge to the next.

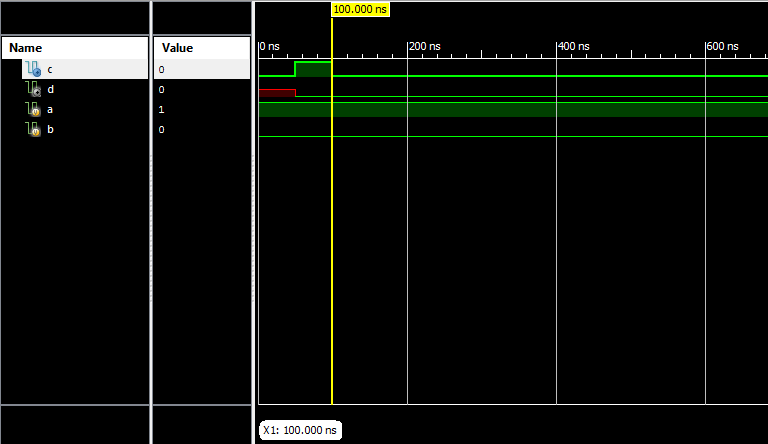

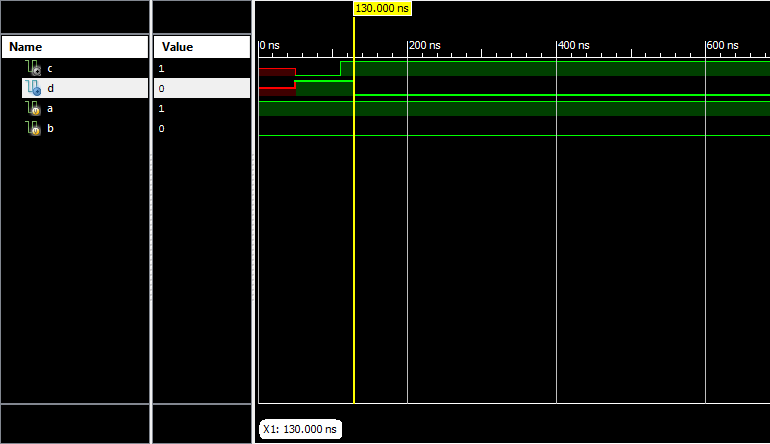

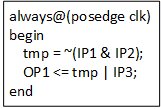

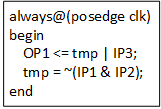

It is good practice to separate combinational and sequential code as much as possible. In verilog, if we want to create sequential logic can use a clocked always block with non-blocking assignments. If on the other hand we want to create combinational logic can use an always block with blocking assignments. Best not to mix the two in the same always block but if they are mixed, need to be careful when doing this. Its up to the synthesis tools to determine whether a blocking assignment within a clocked always block will infer a flip-flop or not. If the signal is read before being assigned (eg fig2 below), the tools will infer sequential logic.

For simplicity purposes only showing in the verilog examples below the Always Block. These Always blocks are blocks of sequential logic since it involves a clock.

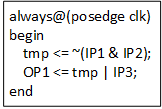

If on an active clock edge, the variable tmp is being assigned a value before it’s value is used (ie ‘write before read’ case) then no flip-flop is required & synthesis will not infer it as shown in fig1 below.

If the value of the reg is used before a new value is assigned to it (ie ‘read before write’ case), then the value that is used will be the value that was assigned on a previous clock. Therefore a flip-flop is required here as shown in fig2 below.

If all non-blocking assignments are used within the always block, it will look like :

Non-blocking assignments always imply flip-flops (order of assignments doesn’t matter). Same block diagram is inferred on both cases as shown in fig3 above. They result in simultaneous or parallel statement execution.

Verilog Tutorial

Verilog code example, what is verilog .

Verilog is a hardware description language (HDL) that is used to describe digital systems and circuits in the form of code. It was developed by Gateway Design Automation in the mid-1980s and later acquired by Cadence Design Systems.

Verilog is widely used for design and verification of digital and mixed-signal systems, including both application-specific integrated circuits (ASICs) and field-programmable gate arrays (FPGAs). It supports a range of levels of abstraction, from structural to behavioral, and is used for both simulation-based design and synthesis-based design.

The language is used to describe digital circuits hierarchically, starting with the most basic elements such as logic gates and flip-flops and building up to more complex functional blocks and systems. It also supports a range of modeling techniques, including gate-level, RTL-level, and behavioral-level modeling.

What was used before Verilog ?

Before the development of Verilog, the primary hardware description language (HDL) used for digital circuit design and verification was VHDL (VHSIC Hardware Description Language). VHDL was developed in the 1980s by the U.S. Department of Defense as part of the Very High-Speed Integrated Circuit (VHSIC) program to design and test high-speed digital circuits.

VHDL is a complex language that enables designers to describe digital systems using a range of abstraction levels, from the low-level transistor and gate levels up to complex hierarchical systems. It was designed to be more descriptive and flexible than earlier HDLs, such as ABEL (Advanced Boolean Expression Language), ISP (Integrated System Synthesis Procedure), and CUPL (Compiler for Universal Programmable Logic).

Despite the development of Verilog and its increasing popularity since the 1980s, VHDL remains a widely used HDL, particularly in Europe and in the military and aerospace industries. Today, both Verilog and VHDL are widely used in digital circuit design and verification, with many companies and organizations using a combination of the two languages.

Why is Verilog better than its predecessor languages ?

Verilog introduced several important improvements over its predecessor languages, which helped make it a more popular and effective HDL for digital circuit design and verification. Here are a few reasons why Verilog is considered better than its predecessor HDLs:

How is Verilog useful ?

Verilog creates a level of abstraction that helps hide away the details of its implementation and technology.

For example, the design of a D flip-flop would require the knowledge of how the transistors need to be arranged to achieve a positive-edge triggered FF and what the rise, fall and clk-Q times required to latch the value onto a flop among many other technology oriented details. Power dissipation, timing and the ability to drive nets and other flops would also require a more thorough understanding of the physical characteristics of a transistor.

Verilog helps us to focus on the behavior and leave the rest to be sorted out later.

The following Verilog code describes the behavior of a counter. The counter counts up if the up_down signal is 1, and down if its value is 0. It also resets the counter if the signal rstn becomes 0, making it an active-low reset.

The simple example shown above illustrates how all the physical implementation details (interconnection of underlying logic gates like NAND and NOR) have been hidden while still providing a clear idea of how the counter functions.

ctr is a module that represents an up/down counter, and it is possible to choose the actual physical implementation of the design from a wide variety of different styles of flops optimized for area, power and performance. They are usually compiled into libraries and will be available for us to select within EDA tools at a later stage in the design process.

How is Verilog different from software languages like C and Java ?

Verilog is a hardware description language (HDL) used to describe digital circuits and systems, while C and Java are software programming languages used to write code that runs on general-purpose computers. Here are some of the main differences between Verilog and programming languages like C and Java:

Overall, Verilog is a specialized language designed specifically for digital circuit design and isn't used for general-purpose programming like C and Java. While there are some similarities in syntax and programming concepts between these languages, the primary focus and application of Verilog is on the design, simulation, and implementation of digital circuits and systems.

What may replace Verilog in the future ?

It's difficult to predict exactly what may replace Verilog in the future, but there are several emerging technologies and languages that may have an impact on the future of digital system design and verification.

One technology that may affect the future of digital system design is High-Level Synthesis (HLS), which is a technique for automatically generating hardware designs from high-level descriptions in languages like C, C++, and SystemC. HLS allows designers to express their design intents and functionality at a higher level of abstraction, rather than specifying the details of logic gates and register transfers in Verilog or VHDL. This could enable more efficient and rapid design of digital systems, and allow designers to explore more design space in a shorter period of time.

Another technology that may impact the future of digital system design is machine learning and artificial intelligence (AI), which have the potential to significantly streamline the design and verification process of digital systems. For example, machine learning algorithms can be used to automatically optimize and generate hardware designs, reducing the need for manual design efforts.

There are also emerging HDLs that are trying to address some of the limitations of Verilog and VHDL, such as Chisel and MyHDL, which are based on more modern programming concepts and provide higher-level abstractions.

COMMENTS

Non-blocking. Non-blocking assignment allows assignments to be scheduled without blocking the execution of following statements and is specified by a = symbol. It's interesting to note that the same symbol is used as a relational operator in expressions, and as an assignment operator in the context of a non-blocking assignment.

Blocking vs. Nonblocking in Verilog. The concept of Blocking vs. Nonblocking signal assignments is a unique one to hardware description languages. The main reason to use either Blocking or Nonblocking assignments is to generate either combinational or sequential logic. In software, all assignments work one at a time. So for example in the C ...

Evaluate b&(~c) but defer assignment of z 1. Evaluate a | b, assign result tox x 2. Evaluate a^b^c, assign result to y 3. Evaluate b&(~c), assign result to zz I. Blocking vs. Nonblocking Assignments • Verilog supports two types of assignments within always blocks, with subtly different behaviors. • Blocking assignment: evaluation and ...

was fairly sure that nonblocking assignments were sequential while blocking assignments were parallel. Blocking assignment executes "in series" because a blocking assignment blocks execution of the next statement until it completes. Therefore the results of the next statement may depend on the first one being completed. Non-blocking assignment ...

Blocking and Non-blocking Assignment in Verilog. When working with behavioural modeling in Verilog, there are two types of assigment which is known as blocking and non blocking assigment and both of them there is a operator, '=' operator for blocking assignment and '=' operator for non blocking assigment.At short, blocking assignment executes one by one sequentially and non-blocking assignemnt ...

Blocking And Nonblocking In Verilog. Blocking Statements: A blocking statement must be executed before the execution of the statements that follow it in a sequential block. In the example below the first time statement to get executed is a = b followed by. Nonblocking Statements: Nonblocking statements allow you to schedule assignments without ...

Blocking assignments. Blocking assignments (=) are done sequentially in the order the statements are written. A second assignment is not started until the preceding one is complete. i.e, it blocks all the further execution before it itself gets executed. Example: Non-Blocking assignments.

The verilog simulator treats = and <= quite differently. Blocking assignments mean 'assign the value to the variable right away this instant'. Nonblocking assignments mean 'figure out what to assign to this variable, and store it away to assign at some future time'.

The blocking assignment statements are executed sequentially by evaluating the RHS operand and finishes the assignment to LHS operand without any interruption from another Verilog statement. Hence, it blocks other assignments until the current assignment completes and is named as "blocking assignment".

Blocking vs Non-Blocking Assignments • Blocking (=) and non-blocking (<=) assignments are provided to control the execution order within an always block. • Blocking assignments literally block the execution of the next statement until the current statement is executed. - Consequently, blocking assignments result in ordered statement ...

Blocking assignment blocks the execution of the next statement until the completion of the current assignment execution. Blocking assignment example. In Below Example, a and b is initialized with value 10 and 15 respectively, after that b is being assigned to a (a value will become 15), and value 20 is assigned to b. After assignment value of a ...

end. There are now two extra states and an else. The else is needed because two dependent blocking assign-ments happen in the first clock cycle, except when the input is 2. In that case, there is only one assignment (of the input to the output). As discussed earlier, equiva-lent non-blocking code requires an if else.

An edge-sensitive intra-assignment timing control permits a special use of the repeat loop. The edge sensitive time control may be repeated several times before the delay is completed. Either the blocking or the non-blocking assignment may be used. always always @(IN) @(IN) OUT OUT <= <= repeat.

Verilog supports blocking and non-blocking assignments statements within the always block with their different behaviors. The blocking assignment is similar to software assignment statements found in most popular programming languages. The non-blocking assignment is the more natural assignment statement to describe many hardware systems ...

20 October 2020. Blocking / Non-Blocking assignment rules. The main reason to use either Blocking or Non-Blocking assignments is to generate either combinational or sequential logic. In non-blocking assignments (<=), all registers inside the always block are updated at the end. In blocking assignments (=), the registers are updated immediately.

of assignment used. There are two types of assignments: <= (non-blocking) and = (blocking). 1.2 <= (non-blocking) Assignments Non-blocking assignments happen in parallel. In other words, if an always@ block contains multiple <= assignments, which are literally written in Verilog sequentially, you should think of all of the assignments

The significance of blocking and non-blocking assignments in Verilog coding cannot be overstated. These elements serve as the foundation for precise and effective digital circuit design, offering ...

The non-blocking assignment allows designers to describe a state-machine update without needing to declare and use temporary storage variables. For example, in this code, when you're using a non-blocking assignment, its action won't be registered until the next clock cycle. ... "<=" is a non-blocking assignment operator in verilog."=" is a ...

Purpose: Verilog is used to describe digital circuits and systems, while C and Java are used to write software programs that run on computers. Syntax: Verilog has a different syntax than C and Java, as it is designed to describe the behavior of digital circuits rather than the execution of software instructions. For example, Verilog describes ...

I understand that with the following Verilog code (snip code example using blocking assignments) It uses non-blocking statements all in parallel and I understand that when this is synthesised, it's basically 3 registers in series and it takes 3 clock cycles for 1'b1 to reach r_Test_3. Careful. Remember the initial state of registers is undefined.

1. You should follow the industry practice which tells you to use non-blocking assignments for all outputs of the sequential logic. The only exclusion are temporary vars which are used to help in evaluation of complex expressions in sequential logic, provided that they are used only in a single block. In you case using 'blocking' for the ...