- Altera Manuals

- Motherboard

- Reference manual

Altera Cyclone II Reference Manual

- page of 56 Go / 56

Table of Contents

About this manual, chapter 1. introduction.

- Hardware Features

- Software Features

- Block Diagram

- JTAG Programming

- AS Programming

- Configuring the FPGA in JTAG Mode

- Configuring the EPCS4 Device in as Mode

- Cyclone II EP2C20 FPGA

- Serial Configuration Device and USB Blaster Circuit

- Flash Memory

- SD Card Socket

- Push Button Switches

- Toggle Switches

- Clock Inputs

- Audio CODEC

- Serial Ports

- Dual 40-Pin Expansion Headers

Chapter 2. Development Board Components

- Component List

- USB-Blaster Controller

- VGA Circuit Pin List

- VGA Circuit Schematic

- Audio Circuit Schematic

- Audio Circuit Pin List

- SDRAM Schematic and Pin List

- SRAM Schematic and Pin List

- Flash Schematic and Pin List

- Clock Circuit Schematic

- Clock Input Pin List

- Power ON/OFF Switch

- RUN/PROG Switch

- Push Button Switch Schematic

- Push Button Switch Pin List

- Toggle Switch Schematic

- Toggle Switch Pin List

- LED Schematic

- LED Pin List

- Seven-Segment Display Schematic

- Seven-Segment Display Pin List

- USB-Blaster Port

- Expansion Header Schematics

- Expansion Header Pin List

- SD Card Connector

- RS-232 Circuit Schematic

- RS-232 Serial Circuit Pin List

- PS/2 Circuit Schematic

- PS/2 Serial Circuit Pin List

- VGA Video Port

- Audio Ports

- SMA External Clock Connector

- Power Supply Connector

Advertisement

Quick Links

Related manuals for altera cyclone ii.

Summary of Contents for Altera Cyclone II

- Page 1 Cyclone II FPGA Starter Development Board Reference Manual 101 Innovation Drive San Jose, CA 95134 (408) 544-7000 Document Version http://www.altera.com Document Date October 2006...

- Page 2 Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Al- tera products are protected under numerous U.S.

Page 3: Table Of Contents

- Page 4 RS-232 Serial Circuit Pin List ....................2–34 PS/2 Port ............................2–34 PS/2 Circuit Schematic ......................2–34 PS/2 Serial Circuit Pin List ...................... 2–34 VGA Video Port ..........................2–35 Audio Ports ............................. 2–35 SMA External Clock Connector ....................2–36 Power Supply Connector ......................2–36 Altera Corporation Preliminary...

Page 5: About This Manual

- Page 6 About This Manual For the most up-to-date information about Altera products, go to the Altera world-wide web site at www.altera.com. For technical support on this product, go to www.altera.com/mysupport. For additional information about Altera products, consult the sources shown below.

- Page 7 The warning indicates information that should be read prior to starting or continuing the procedure or processes The angled arrow indicates you should press the Enter key. The feet direct you to more information on a particular topic. Altera Corporation Reference Manual October 2006 Cyclone II FPGA Starter Development Board...

- Page 8 About This Manual viii Reference Manual Altera Corporation Cyclone II FPGA Starter Development Board October 2006...

Page 9: Chapter 1. Introduction

Page 10: hardware features, page 11: configuring the cyclone ii fpga, page 12: as programming, page 13: configuring the epcs4 device in as mode.

- Page 14 EPCS Serial Configuration Device Component Table 1–1 lists the components, their locations, and brief descriptions. Summary Table 1–1. Cyclone II FPGA Development Board Components & Interfaces (Part 1 of 2) Board Designation Name Description Cyclone II FPGA EP2C20 device User Interface KEY0 –...

Page 15: Component Features

Page 16: serial configuration device and usb blaster circuit, page 17: clock inputs.

- Page 18 Introduction 1–10 Reference Manual Altera Corporation Cyclone II FPGA Starter Development Board October 2006...

Page 19: Chapter 2. Development Board Components

Page 20: usb-blaster controller, page 21: vga timing, page 22: vga circuit pin list, page 23: audio codec, page 24: audio circuit schematic, page 25: audio circuit pin list.

- Page 26 PIN_W4 SDRAM Address[0] DRAM_ADDR[1] PIN_W5 SDRAM Address[1] DRAM_ADDR[2] PIN_Y3 SDRAM Address[2] DRAM_ADDR[3] PIN_Y4 SDRAM Address[3] DRAM_ADDR[4] PIN_R6 SDRAM Address[4] DRAM_ADDR[5] PIN_R5 SDRAM Address[5] DRAM_ADDR[6] PIN_P6 SDRAM Address[6] 2–8 Reference Manual Altera Corporation Cyclone II FPGA Starter Development Board October 2006...

Page 27: Sram Schematic And Pin List

- Page 28 PIN_AB4 SRAM Address[3] SRAM_ADDR[4] PIN_AA5 SRAM Address[4] SRAM_ADDR[5] PIN_AB10 SRAM Address[5] SRAM_ADDR[6] PIN_AA11 SRAM Address[6] SRAM_ADDR[7] PIN_AB11 SRAM Address[7] SRAM_ADDR[8] PIN_V11 SRAM Address[8] SRAM_ADDR[9] PIN_W11 SRAM Address[9] 2–10 Reference Manual Altera Corporation Cyclone II FPGA Starter Development Board October 2006...

Page 29: Flash Schematic And Pin List

- Page 30 PIN_R14 FLASH Address[8] FL_ADDR[9] PIN_Y13 FLASH Address[9] FL_ADDR[10] PIN_R12 FLASH Address[10] FL_ADDR[11] PIN_T12 FLASH Address[11] FL_ADDR[12] PIN_AB14 FLASH Address[12] FL_ADDR[13] PIN_AA13 FLASH Address[13] FL_ADDR[14] PIN_AB13 FLASH Address[14] 2–12 Reference Manual Altera Corporation Cyclone II FPGA Starter Development Board October 2006...

Page 31: Clock Circuit

Page 32: clock input pin list, page 33: power on/off switch, page 34: push button switches, page 35: push button switch schematic, page 36: toggle switch schematic, page 37: toggle switch pin list.

- Page 38 Development Board Components Figure 2–15. LED Schematic Diagram 2–20 Reference Manual Altera Corporation Cyclone II FPGA Starter Development Board October 2006...

Page 39: Led Pin List

Page 40: seven-segment display schematic, page 41: seven-segment display pin list, page 42: connectors, page 43: usb-blaster port, page 44: expansion header schematics.

- Page 45 Development Board Components Figure 2–21. Expansion Header JP1 Schematic Diagram Figure 2–22 shows the JP2 expansion header schematic. Altera Corporation Reference Manual 2–27 October 2006 Cyclone II FPGA Starter Development Board...

Page 46: Expansion Header Pin List

- Page 47 GPIO Connection 0[32] GPIO_0[33] PIN_K20 GPIO Connection 0[33] GPIO_0[34] PIN_L19 GPIO Connection 0[34] GPIO_0[35] PIN_L18 GPIO Connection 0[35] GPIO_1[0] PIN_H12 GPIO Connection 1[0] GPIO_1[1] PIN_H13 GPIO Connection 1[1] Altera Corporation Reference Manual 2–29 October 2006 Cyclone II FPGA Starter Development Board...

- Page 48 GPIO Connection 1[30] GPIO_1[31] PIN_N21 GPIO Connection 1[31] GPIO_1[32] PIN_P15 GPIO Connection 1[32] GPIO_1[33] PIN_N15 GPIO Connection 1[33] GPIO_1[34] PIN_P17 GPIO Connection 1[34] GPIO_1[35] PIN_P18 GPIO Connection 1[35] 2–30 Reference Manual Altera Corporation Cyclone II FPGA Starter Development Board October 2006...

Page 49: Sd Card Connector

Page 50: rs-232 serial port, page 51: rs-232 circuit schematic, page 52: rs-232 serial circuit pin list, page 53: vga video port, page 54: sma external clock connector.

- Page 55 Development Board Components Figure 2–31. Power Supply Connector Altera Corporation Reference Manual 2–37 October 2006 Cyclone II FPGA Starter Development Board...

- Page 56 Development Board Components 2–38 Reference Manual Altera Corporation Cyclone II FPGA Starter Development Board October 2006...

Rename the bookmark

Delete bookmark, delete from my manuals, upload manual.

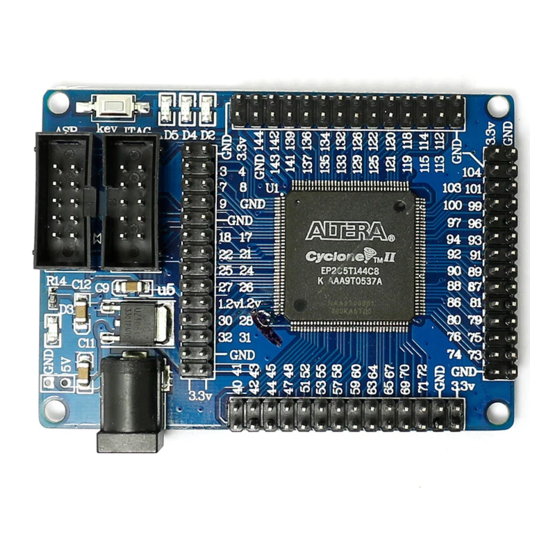

Cyclone II EP2C5 Mini Dev Board

- 2 Part Specific Programming

- 3 I/O Pin Mapping

- 4.1 LEDs and button on EP2C5 Board

- 5 Quartus II Notes

- 6 Requirements

- 9 Pin List (Multicomp)

- EP2C5-DB Multicomp Adapter card

- FPGA part is EP2C5T144C8 (marking is EP2C5T144C8N)

- Ebay listing

- (4) 14x2 headers (0.1" pitch)

- EPCS4 for configuration EPROM (4 Mbit)

- 5V only operation

- 2.1mm DC socket

- 50 MHz crystal oscillator (clock)

- JTAG/SWD connectors

- LED for power indication

Part Specific Programming

- Land Boards GitHub repo

- Quartus II Handbook (pdf)

- Does not remain after power cycling

- Flash EPROM = EPCS4

- Remains after power cycling

I/O Pin Mapping

Onboard leds and button, leds and button on ep2c5 board.

- D2 is on PIN_3

- D4 is on PIN_7

- D5 is on PIN_9

- key is on PIN_144

Pins 26 and 81 are tied to 1.2V and the default selection is to drive all unused pins to GND, making short circuit and that's why the onboard LM1117 1.2V regulator get really hot. You should go to Assignments->Device->Device and Pin Options...->Unused Pins and set it to "As input tri-stated with weak pull-up" (or "... with bus-hold circuitry"). Then everything stays cool.

Quartus II Notes

- Version 13.0 SP1

- Project > Copy Project to create a separate copy of your project, rather than just a revision within the same project

- VHDL Examples

Requirements

- Cyclone II EP2C5 Mini Dev Board - Boards on Ebay

- USB Blaster

- 5V Wall Wart , or

- USB to 5V cable

- Board Schematic Diagram.pdf

- Cyclone II Device Handbook (pdf)

- Cyclone® II EP2C5 Device Pin-out (pdf)

- EP2C5 core board test.zip

- EP2C5T144E Diagrams.zip

- UK101 FPGA based computer

- Case for Altera Cyclone II EP2C5T board

- NIOS II Implementation on Cyclone II EP2C5T board (in spanish)

- Cyclone II FPGA Overview

- Video uses Quartus II 11.1 SP 2

- Breadboard To Cyclone II Wiring

- Cyclone II - Breadboard Inputs and Outputs

- Altera Cyclone II EP2C5T144 FPGA Mini Board

Pin List (Multicomp)

Navigation menu, personal tools.

- View source

- View history

- GitHub Repos

- Retro-Computers

- Raspberry Pi

- BeagleBone Black

- Ham Radio Projects

- Land Board Videos

- Test Equipment

- 3D Printing

- Recent changes

- Random page

- Help about MediaWiki

- What links here

- Related changes

- Special pages

- Printable version

- Permanent link

- Page information

- This page was last edited on 25 June 2021, at 19:45.

- Privacy policy

- About Land Boards Wiki

- Disclaimers

DE1 I/O Pins

Clocks, buttons, switches, and seven segment displays.

The Cyclone II EP2C20F484C7 FPGA on the DE1 logic kit is connected to four seven segment displays, (Hex_0, Hex_1, Hex_2, and Hex_3), ten slide switches (Switch_0 through Switch_9), four push buttons (Key_0 through Key_3), ten red LEDs (Red_LED_0 through Red_LED_9), and eight green LEDs (Green_LED_0 through Green_LED_7).

The slide switches produce logic “1” when pushed away from the edge of the board, and the push buttons produce logic “0” when pressed. The segments of the seven segment displays light up when connected to logic “0,” and the LEDs light up when connected to logic “1”. The following table shows which FPGA pin numbers are connected to these devices.

The segments of a seven-segment display are normally named A–G, starting at the top, going clockwise, and ending with the center segment. The array names in the table refer to the segments using subscript values 0–6 in the same order.

To make the process of pin assignment easier, the following table is in alphabetical order, which should match the order of the pins listed by the Quartus Pin Assignment Editor, provided you name your pins and pin groups alphabetically: Clock… , Green… , Hex_0… , Hex_1… , Hex_2… , Hex_3… , Key… , Red… , and Switch… in that order.

Success! Subscription added.

Success! Subscription removed.

Sorry, you must verify to complete this action. Please click the verification link in your email. You may re-send via your profile .

- Intel Community

- Product Support Forums

- FPGA, SoC, And CPLD Boards And Kits

Need a pin assignments for kit FPGA Cyclone IV EP4CE6E22C8N

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Printer Friendly Page

- Mark as New

- Report Inappropriate Content

- All forum topics

- Previous topic

Link Copied

Community support is provided during standard business hours (Monday to Friday 7AM - 5PM PST). Other contact methods are available here .

Intel does not verify all solutions, including but not limited to any file transfers that may appear in this community. Accordingly, Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

For more complete information about compiler optimizations, see our Optimization Notice .

- ©Intel Corporation

- Terms of Use

- *Trademarks

- Supply Chain Transparency

- Search forums

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

Welcome to EDAboard.com

Welcome to our site edaboard.com is an international electronics discussion forum focused on eda software, circuits, schematics, books, theory, papers, asic, pld, 8051, dsp, network, rf, analog design, pcb, service manuals... and a whole lot more to participate you need to register. registration is free. click here to register now..

- Digital Design and Embedded Programming

- PLD, SPLD, GAL, CPLD, FPGA Design

Altera CycloneII Bidirectional Pin Assignment

- Thread starter nag123

- Start date Sep 16, 2008

- Sep 16, 2008

Member level 1

altera bidirectional Hi all, I am new to altera FPGA design. I have got a problem on bidirectional io pin assignment. I have interfaced Altera CyclonII FPGA with a processor. The processor is able to write the data to FPGA. It's not reading FPGA data. All control srtrobes rd_en, wr_en and cs are ok. I have a doubt whether I assigned data bus correctly or not. Can anyone suggest me how to assign bidirectional pins? Do I need to set any constraint in assignment editor? Thanks

Member level 5

@ltera CycloneII Bidirectional Pin Assignment You don't need any FPGA constraint, but it's pure VHDL code. In the FPGA you can always read the data so DATA_IN <= CPU_DATA_BUS; But you need to set the bus in treestate when you don't need to write (in this example CS is active high, so when it's active you can put your data out else you need to keep the bus in treestate). CPU_DATA_BUS <= DATA_TO_OUT when (CS='1') else (others => 'Z'); Hope it helps

- Oct 22, 2008

karikalan_t79

Full member level 1.

check the pin planner , does it correctly instatiate bidir pin for the particular pin, otherwise, just add it

Similar threads

- Started by hexaeder

- Mar 18, 2024

- Started by latebird

- Feb 22, 2022

- Started by Oscar99haha

- Jul 31, 2022

- Started by matrixofdynamism

- Dec 13, 2022

- Started by stark43

- Sep 27, 2022

Part and Inventory Search

Welcome to edaboard.com.

- This site uses cookies to help personalise content, tailor your experience and to keep you logged in if you register. By continuing to use this site, you are consenting to our use of cookies. Accept Learn more…

IMAGES

VIDEO

COMMENTS

Pin Name Pin Type (1st, 2nd, and 3rd Function) Pin Description Connection Guidelines. Pin Information for the Cyclone®II EP2C5 Device Version 2.0. Note (1) LVDS[0-256][p,n](Note 3)I/O, TX/RX channel Dual-purpose differential transmitter/receiver channels 0 to 256.

1-2 Altera Corporation Cyclone II Device Handbook, Volume 1 July 2005 Features and PCI-X 1.0, 3.3-, 2.5-, 1.8-, and 1.5-V LVCMOS, and 3.3-, 2.5-, ... within the Quartus® II software (go to Assignments menu, then Device, then click the Migration Devices button). After compilation, check the ... Cyclone II Device Speed Grades Device 144-Pin ...

SMA external clock connector 7.5 V power supply connector Cyclone II The main device that defines the starter development board is an Altera ® Cyclone II EP2C20 FPGA in a 484-pin FineLine BGA package. Table 2-1 EP2C20 FPGA lists the FPGA features. Page 20: Usb-Blaster Controller

2 Answers. There are two ways of specifying PIN assignment — you can either use PinPlanner or to specify the PIN along with to specify the IO standard. I recommend you read I/O Management documentation from Altera. But here are few examples: These are location assignments for 1 GbE RGMII Ethernet Interface:

This is a tutorial on how to assign the Input & Output of your HDL code to an Intel Altera Cyclone II FPGA pins using Intel Altera Qaurtus II version 13 usin...

Launch the Quartus II software: All programs → Altera → Quartus II 10.0 Web Edition → Quartus II Web Edition; Click Create a New Project, when Wizard window pops up. Or select File → New Project Wizard → Next; Choose the Directory and name of the project: Working directory: Choose the E: where your flash disk will be.

The Cyclone II FPGA Starter board includes a video connector (Figure 2-28) that connects to an on-board 4-bit video DAC. The connector is a standard DB15 15-pin analog VGA connector. Refer to "VGA DAC" on page 2-2 for a description of the circuitry attached to this connector. Figure 2-28.

Altera DE2 Board Pin Table SRAM_WE_N PIN_AE10 SRAM Write Enable SRAM_OE_N PIN_AD10 SRAM Output Enable SRAM_UB_N PIN_AF9 SRAM High-byte Data Mask SRAM_LB_N PIN_AE9 SRAM Low-byte Data Mask SRAM_CE_N PIN_AC11 SRAM Chip Enable Signal Name FPGA Pin No. Description OTG_ADDR[0] PIN_K7 ISP1362 Address[0]

32. Choose Assignments → Pins, which opens the Pin Planner, a spreadsheet-like table of specific pin assignments. The Pin Planner shows the design's pins. 33. In the Location column next to each of the node names, add the coordinates (pin numbers) for the actual values to use with the board. For the pin layout of components on

LEDs and button on EP2C5 Board. D2 is on PIN_3. D4 is on PIN_7. D5 is on PIN_9. key is on PIN_144. Pins 26 and 81 are tied to 1.2V and the default selection is to drive all unused pins to GND, making short circuit and that's why the onboard LM1117 1.2V regulator get really hot.

yzdnisr. I am quite new to FPGA and I want to design a 1-digit counter on a 7-segment on an Altera development board. What I have done so far was to schematically design a bcd to 7-segment decoder in Quartus as displayed in the image below. I am quite puzzled about how I can assign the pin "SEG0" and not all the 4 7-segments I have on the board ...

The Cyclone II EP2C20F484C7 FPGA on the DE1 logic kit is connected to four seven segment displays, (Hex_0, Hex_1, Hex_2, and Hex_3), ten slide switches (Switch_0 through Switch_9), four push buttons (Key_0 through Key_3), ten red LEDs (Red_LED_0 through Red_LED_9), and eight green LEDs (Green_LED_0 through Green_LED_7). The slide switches ...

Page 1 of 1. Cyclone® V Device Family Pin Connection Guidelines Preliminary PCG-01014-1.2. Altera recommends that you create a Quartus® II design, enter your device I/O assignments, and compile the design. The Quartus II software will check your pin connections according to I/O assignment and placement rules.

Dear Altera, My name is Phu Nguyen. I am looking for a file pin assignment for kit FPGA Cyclone IV EP4CE6E22C8N. I used to use kit DE2 and have a file exel DE2_pin_assignment but i can't find a file for kit FPGA Cyclone IV EP4CE6E22C8N. Can you give me or link of file pin assignment for kit FPGA Cyclone IV EP4CE6E22C8N.

Two 40-pin expansion headers • 72 Cyclone II I/O pins, as well as 8 power and ground lines, are brought out to two 40-pin expansion connectors • 40-pin header is designed to accept a standard 40-pin ribbon cable used for IDE hard drives • Resistor protection is provided 2.3 Power-up the DE1 Board

Member level 1. I am new to altera FPGA design. I have got a problem on bidirectional io pin assignment. I have interfaced Altera CyclonII FPGA with a processor. The processor is able to write the data to FPGA. It's not reading FPGA data. All control srtrobes rd_en, wr_en and cs are ok.