If Statements and Case Statements in Verilog

In this post we talk about two of the most commonly used constructs in verilog - the if statement and the case statement.

We have seen in a previous post how use procedural blocks such as the always block to write verilog code which is executed sequentially .

We can also use a number of statements within procedural blocks which control the way that signals are assigned in our verilog designs. Collectively, these statements are known as sequential statements.

The case statement and the if statement are both examples of sequential statements in verilog.

In the rest of this post, we talk about how both of these statements are used in verilog. We then consider a short example for both of these constructs to show how we use them in practise.

Verilog If Statement

The if statement is a conditional statement which uses boolean conditions to determine which blocks of verilog code to execute.

Whenever a condition evaluates as true, the code branch associated with that condition is executed.

This statement is similar to if statements used in other programming languages such as C.

The verilog code snippet below shows the basic syntax for the if statement.

We can exclude the else and else if branches from the statement if we don't need them.

In fact, we have already seen this in the post on always blocks where we used the posedge macro to detect the rising edge of a clock signal.

We can include as many else if branches as necessary to properly model the underlying circuit.

The if statement uses boolean conditions to determine which lines of code to execute.

In the snippet above, these expressions are given by <expression1> and <expression2>.

These expressions are sequentially evaluated and the code associated with the expression is executed if it evaluates to true.

Only one branch of an if statement will ever execute. This is normally the first expression which evaluates as true.

The only exception to this occurs when none of the expressions are true. In this instance, the code in the else branch will execute.

When we omit the else branch in our if statement code then none of the branches will execute in this case.

The code associated with each branch can include any valid verilog code, including further if statements. This approach is known as nested if statements.

When using this type of code in verilog, we should take care to limit the number of nested statements as it can lead to difficulties in meeting timing.

- If Statement Example

We have already seen a practical example of the if statement when modelling flip flops in the post on the verilog always block .

To demonstrate this construct more thoroughly, let's consider an example of a clocked multiplexor.

In this instance, we will use an asynchronously resettable D type flip flop to register the output of a multiplexor .

The circuit diagram below shows the circuit which we will use in this example.

The code snippet below shows how we implement this using a single always block and an if statement.

In this example, we use the first if statement to set the output of the flip flop to 0b whenever reset is active.

When the reset is not active, then the always block has been triggered by the rising edge of the clock. We use the else branch of the first if statement to capture this condition.

We use a second if statement to model the behaviour of the multiplexor circuit. This is an example of a nested if statement in verilog.

When the addr signal is 0b, we assign the output of the flip flop to input a. We use the first branch of the nested if statement to capture this condition.

We then use the else branch of the nested if statement to capture the case when the addr signal is 1b.

It is also possible for us to use an else-if type statement here but the else statement is more succinct. The behaviour is the same in both cases as the signal can only ever be 0b or 1b in a real circuit.

Verilog Case Statement

We use the verilog case statement to select a block of code to execute based on the value of a given signal in our design.

When we write a case statement in verilog we specify an input signal to monitor and evaluate.

The value of this signal is then compared with the values specified in each branch of the case statement.

Once a match is found for the input signal value, the branch associated with that value will execute.

The verilog case statement performs the same function as the switch statement in the C programming language.

The code snippet below shows the general syntax for the case statement in verilog.

It is possible to exclude the default branch of the statement, although this is not advisable. If the default branch is excluded then all valid values of the <variable> must have it's own branch.

As with the if statement, the code associated with each branch can include any valid verilog code.

This includes further sequential statements, such as if or case statements. Again, we should try to limit the number of nested statements as it makes it easier to meet our timing requirements.

- Case Statement Example

To better demonstrate the way we use the case statement in verilog, let's consider a basic example.

For this example we will look at a simple four to one multiplexor circuit.

We frequently use the case statement to model large multiplexors in verilog as it produces more readable code than continuous assignment based implementations.

The code snippet below shows how we would implement this circuit using a case statement.

This example shows how simple it is to model a multiplexor using the case statement in verilog. In fact, the case statement provides the most intuitive way of modelling a multiplexor in verilog.

Although this example is quite straight forward, there are a few important points which we should consider in more detail.

The first thing to note in this example is that we use blocking assignment . The reason for this is that we are modelling combinational logic and non-blocking assignment normally leads to flip flops being placed in our design.

Another thing to note here is that we could remove the default keyword from this example. We would then explicitly list the value of addr required to output the value of d instead.

However, we have included the default keyword in this example to demonstrate how it should be used.

Which blocks do we use to write sequential statements in a verilog design?

Sequential statements can only be written within a procedural block such as an always block or initial block.

Which keywords can we exclude from the if statement when they are not required?

We can exclude the else and else if keywords if they are not needed.

How many branches of the if statement can be executed at one time?

A maximum of one branch in an if statement can execute at any time.

When can we exclude the default branch from the case statement?

We can exclude the default branch if all valid values of the input signal are explicitly listed.

Use a case statement to write the code for a six to one multiplexor.

Rewrite the six to one multiplexor from the last exercise so that it uses an if statement.

One comment on “If Statements and Case Statements in Verilog”

clearly explained with nice examples the style of the web page is also nice

Leave a Reply Cancel reply

Your email address will not be published. Required fields are marked *

Save my name, email, and website in this browser for the next time I comment.

Table of Contents

Sign up free for exclusive content.

Don't Miss Out

We are about to launch exclusive video content. Sign up to hear about it first.

- The Verilog-AMS Language

- Analog Processes

- Conditional Statements

Conditional Statements

If statements .

An if statement evaluates an expression and executes the subsequent statement if the expression evaluates to true, otherwise it skips that statement. For example:

An if/else statement evaluates an expression and executes the statement before else if the expression evaluates to true, otherwise it evaluates the statement after the else . For example:

A common idiom is to nest if/else statements as follows:

In this case an if keyword binds to the next closest else keyword.

Case Statements

A case statement tests and expression and then enumerates what actions should be taken for the various values that expression can take. For example:

If the needed case is not found, then no statements are executed. If multiple cases are found that match, the first one found is used (they are tried in order). If more that once cases should be associated with the same statement, they can be given in a comma separated list:

It is also possible to specify a default case:

?: conditional operator in Verilog

Compact conditional operators.

Many Verilog designs make use of a compact conditional operator:

A comman example, shown below, is an “enable” mask. Suppose there is some internal signal named a . When enabled by en== 1 , the module assigns q = a , otherwise it assigns q = 0 :

The syntax is also permitted in always blocks:

Assigned Tasks

This assignment uses only a testbench simulation, with no module to implement. Open the file src/testbench.v and examine how it is organized. It uses the conditional operator in an always block to assign q = a^b (XOR) when enabled, else q= 0 .

Run make simulate to test the operation. Verify that the console output is correct. Then modify the testbench to use an assign statement instead of an always block . Change the type of q as appropriate for the assign statement.

Turn in your work using git :

Indicate on Canvas that your assignment is done.

Combinational Logic with assign

The verilog assign statement is typically used to continuously drive a signal of wire datatype and gets synthesized as combinational logic. Here are some more design examples using the assign statement.

Example #1 : Simple combinational logic

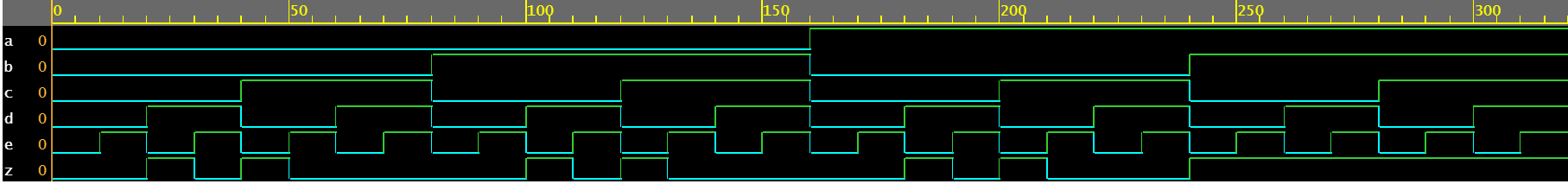

The code shown below implements a simple digital combinational logic which has an output wire z that is driven continuously with an assign statement to realize the digital equation.

The module combo gets elaborated into the following hardware schematic using synthesis tools and can be seen that the combinational logic is implemented with digital gates.

The testbench is a platform for simulating the design to ensure that the design does behave as expected. All combinations of inputs are driven to the design module using a for loop with a delay statement of 10 time units so that the new value is applied to the inputs after some time.

Example #2: Half Adder

The half adder module accepts two scalar inputs a and b and uses combinational logic to assign the outputs sum and carry bit cout . The sum is driven by an XOR between a and b while the carry bit is obtained by an AND between the two inputs.

Example #3: Full Adder

A full adder can be built using the half adder module shown above or the entire combinational logic can be applied as is with assign statements to drive the outputs sum and cout .

Example #4: 2x1 Multiplexer

The simple 2x1 multiplexer uses a ternary operator to decide which input should be assigned to the output c . If sel is 1, output is driven by a and if sel is 0 output is driven by b .

Example #5: 1x4 Demultiplexer

The demultiplexer uses a combination of sel and f inputs to drive the different output signals. Each output signal is driven by a separate assign statement. Note that the same signal is generally not recommended to be driven by different assign statements.

Example #6: 4x16 Decoder

Verilog Conditional Operator

Just what the heck is that question mark doing.

Have you ever come across a strange looking piece of Verilog code that has a question mark in the middle of it? A question mark in the middle of a line of code looks so bizarre; they’re supposed to go at the end of sentences! However in Verilog the ? operator is a very useful one, but it does take a bit of getting used to.

The question mark is known in Verilog as a conditional operator though in other programming languages it also is referred to as a ternary operator , an inline if , or a ternary if . It is used as a short-hand way to write a conditional expression in Verilog (rather than using if/else statements). Let’s look at how it is used:

Here, condition is the check that the code is performing. This condition might be things like, “Is the value in A greater than the value in B?” or “Is A=1?”. Depending on if this condition evaluates to true, the first expression is chosen. If the condition evaluates to false, the part after the colon is chosen. I wrote an example of this. The code below is really elegant stuff. The way I look at the question mark operator is I say to myself, “Tell me about the value in r_Check. If it’s true, then return “HI THERE” if it’s false, then return “POTATO”. You can also use the conditional operator to assign signals , as shown with the signal w_Test1 in the example below. Assigning signals with the conditional operator is useful!

Nested Conditional Operators

There are examples in which it might be useful to combine two or more conditional operators in a single assignment. Consider the truth table below. The truth table shows a 2-input truth table. You need to know the value of both r_Sel[1] and r_Sel[0] to determine the value of the output w_Out. This could be achieved with a bunch of if-else if-else if combinations, or a case statement, but it’s much cleaner and simpler to use the conditional operator to achieve the same goal.

Learn Verilog

Leave A Comment Cancel reply

Save my name, email, and website in this browser for the next time I comment.

IMAGES

VIDEO

COMMENTS

11. wire s can only be assigned by assign statements, which can not be used with if statements. If you change x to reg type, then you will be able to assign it in an always block. This will synthesize exactly the same, a common misconception is that a reg type variable implies a register, but it just changes the way the value is assigned.

Verilog assign statement. Signals of type wire or a similar wire like data type requires the continuous assignment of a value. For example, consider an electrical wire used to connect pieces on a breadboard. As long as the +5V battery is applied to one end of the wire, the component connected to the other end of the wire will get the required ...

Then you can also give your intermediate signals intelligible names, further improving maintainability... - vicatcu. Apr 10, 2012 at 12:22. 2. Also, many people avoid it in C-family programming languages, but to be proficient in Verilog you must become familiar with the ternary operator ?:. - The Photon.

In Verilog, conditional statements are used to control the flow of execution based on certain conditions. There are several types of conditional statements in Verilog listed below. Conditional Operator <variable> = <condition> ? <expression_1> : <expression_2>; The conditional operator allows you to assign a value to a variable based on a ...

Verilog if-else-if. This conditional statement is used to make a decision on whether the statements within the if block should be executed or not. If there is an else statement and expression is false then statements within the else block will be executed.

We use the else branch of the first if statement to capture this condition. We use a second if statement to model the behaviour of the multiplexor circuit. This is an example of a nested if statement in verilog. When the addr signal is 0b, we assign the output of the flip flop to input a.

Blocking Assignment. A blocking assignment evaluates the expression on its right hand side and then immediately assigns the value to the variable on its left hand side: a = b + c; It is also possible to add delay to a blocking assignment. For example: a = #10 b + c; In this case, the expression on the right hand side is evaluated and the value ...

A case statement tests and expression and then enumerates what actions should be taken for the various values that expression can take. For example: case (sel) 0: out = in0; 1: out = in1; 2: out = in2; 3: out = in3; endcase. If the needed case is not found, then no statements are executed.

The LHS of an assign statement cannot be a bit-select, part-select or an array reference but can be a variable or a concatenation of variables. reg q; initial begin assign q = 0; #10 deassign q; end force release. These are similar to the assign - deassign statements but can also be applied to nets and variables. The LHS can be a bit-select of ...

The first verilog example does the job but it takes a bit to understand the logic. Please keep in mind I am not complaining about or criticizing any language, I just want to know how to improve code readability for this particular case.

Non-blocking statements in Verilog work in the following fashion: The expressions on the right-hand side get evaluated sequentially but they do not get assigned immediately. The assignment takes place at the end of the time step. In your example, clk_counter + 1 is evaluated but not assigned to clk_counter right away.

Assigned Tasks. This assignment uses only a testbench simulation, with no module to implement. Open the file src/testbench.v and examine how it is organized. It uses the conditional operator in an always block to assign q = a^b (XOR) when enabled, else q= 0.. Run make simulate to test the operation. Verify that the console output is correct.

13. assign is used for driving wire/net type declarations. Since wires change values according to the value driving them, whenever the operands on the RHS changes,the value is evaluated and assigned to LHS ( thereby simulating a wire). Continuous assignments drive values into the nets whenever the right-hand side value changes, hence continuous ...

The verilog assign statement is typically used to continuously drive a signal of wire datatype and gets synthesized as combinational logic. Here are some more design examples using the assign statement.. Example #1 : Simple combinational logic. The code shown below implements a simple digital combinational logic which has an output wire z that is driven continuously with an assign statement to ...

@newbie: I don't think if-else versus conditional assignment affect synthesis. When it comes to debugging, it is much easier to set breakpoints on different sections of a nested if-else statement, but a conditional assignment is usually considered a single break point.

I want to understand the if else if priority and working for Verilog. In my code I can't seem to get to the 3rd condition and statement of the if else if construct. Why? module alu #(parameter WIDT...

The question mark is known in Verilog as a conditional operator though in other programming languages it also is referred to as a ternary operator, an inline if, or a ternary if. It is used as a short-hand way to write a conditional expression in Verilog (rather than using if/else statements). Let's look at how it is used:

I have to build a circuit of an arithmetic right shift operator in verilog and include it in a verilog code of a simple computer. ... If a condition is met assign the wire to whatever signal you are controlling. Otherwise assign some other signal. ... The inputs to the multiplexer are the module_output_wire and something_else, the select signal ...

I believe the issue is with your order of operation. always_comb blocks execute procedurally, top to bottom. In simulation, Z is updated first with the existing value of Result (from the previous time the always block was executed). The Result is updated and Z is not re-evaluated.Result is not part of the sensitivity list because it is a left-hand value. . Therefore, Z will not get updated ...

1. If we assign something to a register ( or do anything else ) in a specific clock cycle, is this assignment performed in the current clock cycle or the next cycle? (Setting: Xilinx , Spartan-3. coded by Verilog via ISE Webpack) Example: foo<= bar; // foo is equal to bar in this cycle or next? foo<= bar; // foo is equal to bar in this cycle or ...