Blocking (immediate) and Non-Blocking (deferred) Assignments in Verilog

There are Two types of Procedural Assignments in Verilog.

- Blocking Assignments

- Nonblocking Assignments

To learn more about Delay: Read Delay in Assignment (#) in Verilog

Blocking assignments

- Blocking assignments (=) are done sequentially in the order the statements are written.

- A second assignment is not started until the preceding one is complete. i.e, it blocks all the further execution before it itself gets executed.

Non-Blocking assignments

- Nonblocking assignments (<=), which follow each other in the code, are started in parallel.

- The right hand side of nonblocking assignments is evaluated starting from the completion of the last blocking assignment or if none, the start of the procedure.

- The transfer to the left hand side is made according to the delays. An intra- assignment delay in a non-blocking statement will not delay the start of any subsequent statement blocking or non-blocking. However normal delays are cumulative and will delay the output.

- Non-blocking schedules the value to be assigned to the variables but the assignment does not take place immediately. First the rest of the block is executed and the assignment is last operation that happens for that instant of time.

To learn more about Blocking and Non_Blocking Assignments: Read Synthesis and Functioning of Blocking and Non-Blocking Assignments

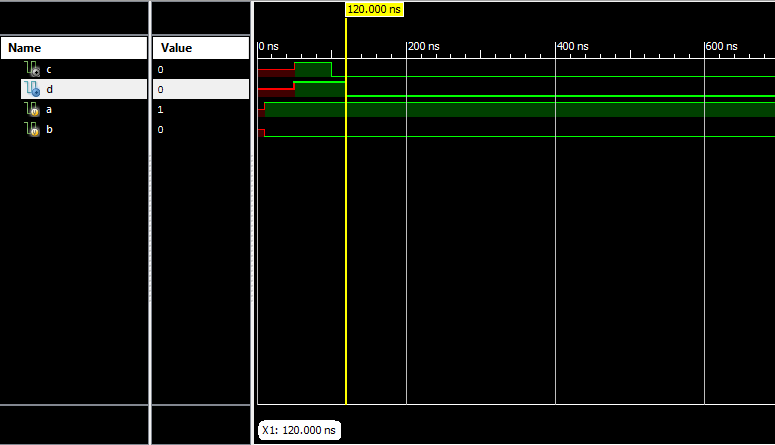

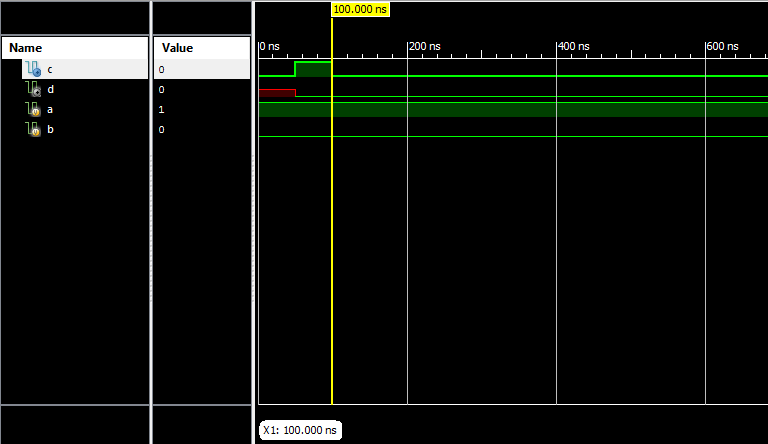

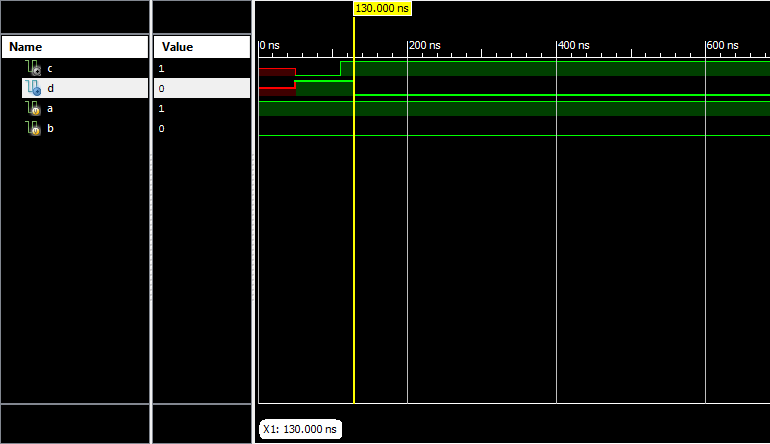

The following example shows interactions between blocking and non-blocking for simulation only (not for synthesis).

For Synthesis (Points to Remember):

- One must not mix “<=” or “=” in the same procedure.

- “<=” best mimics what physical flip-flops do; use it for “always @ (posedge clk..) type procedures.

- “=” best corresponds to what c/c++ code would do; use it for combinational procedures.

Spread the Word

- Click to share on Facebook (Opens in new window)

- Click to share on Twitter (Opens in new window)

- Click to share on LinkedIn (Opens in new window)

- Click to share on Pinterest (Opens in new window)

- Click to share on Tumblr (Opens in new window)

- Click to share on Pocket (Opens in new window)

- Click to share on Reddit (Opens in new window)

- Click to email a link to a friend (Opens in new window)

- Click to print (Opens in new window)

Related posts:

- Synthesis and Functioning of Blocking and Non-Blocking Assignments.

- Delay in Assignment (#) in Verilog

- Ports in Verilog Module

- Module Instantiation in Verilog

Post navigation

Leave a reply cancel reply.

Your email address will not be published. Required fields are marked *

Save my name, email, and website in this browser for the next time I comment.

Notify me of follow-up comments by email.

Notify me of new posts by email.

Verilog Blocking & Non-Blocking

Blocking assignment statements are assigned using = and are executed one after the other in a procedural block. However, this will not prevent execution of statments that run in a parallel block.

Note that there are two initial blocks which are executed in parallel when simulation starts. Statements are executed sequentially in each block and both blocks finish at time 0ns. To be more specific, variable a gets assigned first, followed by the display statement which is then followed by all other statements. This is visible in the output where variable b and c are 8'hxx in the first display statement. This is because variable b and c assignments have not been executed yet when the first $display is called.

In the next example, we'll add a few delays into the same set of statements to see how it behaves.

Non-blocking

Non-blocking assignment allows assignments to be scheduled without blocking the execution of following statements and is specified by a symbol. It's interesting to note that the same symbol is used as a relational operator in expressions, and as an assignment operator in the context of a non-blocking assignment. If we take the first example from above, replace all = symobls with a non-blocking assignment operator , we'll see some difference in the output.

See that all the $display statements printed 'h'x . The reason for this behavior lies in the way non-blocking assignments are executed. The RHS of every non-blocking statement of a particular time-step is captured, and moves onto the next statement. The captured RHS value is assigned to the LHS variable only at the end of the time-step.

So, if we break down the execution flow of the above example we'll get something like what's shown below.

Next, let's use the second example and replace all blocking statements into non-blocking.

Once again we can see that the output is different than what we got before.

If we break down the execution flow we'll get something like what's shown below.

Non Blocking Proceduaral assignments

The non-blocking assignment statement starts its execution by evaluating the RHS operand at the beginning of a time slot and schedules its update to the LHS operand at the end of a time slot. Other Verilog statements can be executed between the evaluation of the RHS operand and the update of the LHS operand. As it does not block other Verilog statement assignments, it is called a non-blocking assignment.

A less than or equal to ‘<=’ is used as a symbol for the non-blocking assignment operator.

- If <= symbol is used in an expression then it is interpreted as a relational operator.

- If <= symbol is used in an assignment then it is interpreted as a non blocking operator.

How race around condition is resolved in a nonblocking assignment?

If a variable is used in LHS of blocking assignment in one procedural block and the same variable is used in RHS of another blocking assignment in another procedural block.

In this example,

Since procedural blocks (both initial and always) can be executed in any order.

In a non-blocking assignment statement no matter what is the order of execution, both RHS of the assignments (y <= data and data <= y) are evaluated at the beginning of the timeslot and LHS operands are updated at the end of a time slot. Thus, race around condition is avoided as there is no dependency on execution order and the order of execution of these two statements can be said to happen parallelly.

Verilog procedural assignment guidelines

For a beginner in Verilog, blocking and non-blocking assignments may create confusion. If are used blindly, it may create race conditions or incorrect synthesizable design. Hence, it is important to understand how to use them. To achieve synthesized RTL correctly, Verilog coding guidelines for blocking and non-blocking assignments are mentioned below

- Use non-blocking assignments for modeling flip flops, latches, and sequential logic.

- Use blocking assignment to implement combinational logic in always block.

- Use non-blocking assignment to implement sequential logic in always block.

- Do not mix blocking and non-blocking assignments in single always block i.e. For the implementation of sequential and combination logic in a single ‘always’ block, use non-blocking assignments.

- Do not assign value to the same variable in the different procedural blocks.

- Use non-blocking assignments while modeling both combination and sequential logic within the same always block.

- Avoid using #0 delay in the assignments.

Verilog Tutorials

Non-synthesizable Verilog Constructs and Testbenches

- First Online: 01 November 2021

Cite this chapter

- Vaibbhav Taraate 2

2177 Accesses

The chapter discusses about the inter-delay, intra-delay assignments and other non-synthesizable constructs useful during the testbenches. The chapter is useful to understand about the non-synthesizable constructs and how to check for the functional correctness of the design.

This is a preview of subscription content, log in via an institution to check access.

Access this chapter

- Available as EPUB and PDF

- Read on any device

- Instant download

- Own it forever

- Compact, lightweight edition

- Dispatched in 3 to 5 business days

- Free shipping worldwide - see info

- Durable hardcover edition

Tax calculation will be finalised at checkout

Purchases are for personal use only

Institutional subscriptions

Author information

Authors and affiliations.

1 Rupee S T (Semiconductor Training @ Rs.1), Pune, Maharashtra, India

Vaibbhav Taraate

You can also search for this author in PubMed Google Scholar

Corresponding author

Correspondence to Vaibbhav Taraate .

Rights and permissions

Reprints and permissions

Copyright information

© 2022 The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this chapter

Taraate, V. (2022). Non-synthesizable Verilog Constructs and Testbenches. In: Digital Logic Design Using Verilog. Springer, Singapore. https://doi.org/10.1007/978-981-16-3199-3_15

Download citation

DOI : https://doi.org/10.1007/978-981-16-3199-3_15

Published : 01 November 2021

Publisher Name : Springer, Singapore

Print ISBN : 978-981-16-3198-6

Online ISBN : 978-981-16-3199-3

eBook Packages : Engineering Engineering (R0)

Share this chapter

Anyone you share the following link with will be able to read this content:

Sorry, a shareable link is not currently available for this article.

Provided by the Springer Nature SharedIt content-sharing initiative

- Publish with us

Policies and ethics

- Find a journal

- Track your research

IMAGES

VIDEO

COMMENTS

Non-Blocking assignments. Nonblocking assignments (<=), which follow each other in the code, are started in parallel. The right hand side of nonblocking assignments is evaluated starting from the completion of the last blocking assignment or if none, the start of the procedure. The transfer to the left hand side is made according to the delays.

Evaluate b&(~c) but defer assignment of z 1. Evaluate a | b, assign result tox x 2. Evaluate a^b^c, assign result to y 3. Evaluate b&(~c), assign result to zz I. Blocking vs. Nonblocking Assignments • Verilog supports two types of assignments within always blocks, with subtly different behaviors. • Blocking assignment: evaluation and ...

An intra-assignment delay is one where there is a delay on the RHS of the assignment operator. This indicates that the statement is evaluated and values of all signals on the RHS is captured first. Then it is assigned to the resultant signal only after the delay expires. module tb;

SNUG Boston 2002 Verilog Nonblocking Assignments Rev 1.4 With Delays, Myths & Mysteries 44 11.6 The 20,000 flip-flop benchmark with #1 delays in the I/O flip-flops All of the preceding mixed RTL and gate-level simulation problems can be traced to signals becoming skewed while crossing module boundaries.

The RHS of every non-blocking statement of a particular time-step is captured, and moves onto the next statement. The captured RHS value is assigned to the LHS variable only at the end of the time-step. Simulation Log. ncsim> run. [0] a= 0xx b= 0xx c= 0xx. [0] a= 0xx b= 0xx c= 0xx. [0] a= 0xx b= 0xx c= 0xx.

Adding delays to the left hand side (LHS) of any sequence of blocking assignments to model combinational logic is also flawed. The adder_t7a example shown in Figure 4 places the delay on the first blocking assignment and no delay on the second assignment. This will have the same flawed behavior as the adder_t1 example.

An edge-sensitive intra-assignment timing control permits a special use of the repeat loop. The edge sensitive time control may be repeated several times before the delay is completed. Either the blocking or the non-blocking assignment may be used. always always @(IN) @(IN) OUT OUT <= <= repeat.

The one exception is a blocking assignment with timing delays on the RHS of the blocking operator, which is considered to be a poor coding style [3]. Execution of blocking assignments can be viewed as a one-step process: ... Verilog blocking and nonblocking assignments function. The "stratified event queue" is a fancy

They produce different output when in toggles before the #5 delay is up. The non-blocking assignment will always delay in by #5 regardless of how fast in toggles. Examples on EDA Playground. Note the difference in sim output. Blocking assignment; Non-Blocking assignment

Blocking assignment (clk = ~ clk; // testbench posedge clk) Triggers evaluation of RHS of sequential logic NBAs ... Simple delay buffer model (delaybuf .v ) Verilog buffer primitive a y 5ns 5ns specify block delay from a -to- y. 18 of 67 Sunburst Design Inertial & Transport Delays commands & displays Reference

was fairly sure that nonblocking assignments were sequential while blocking assignments were parallel. Blocking assignment executes "in series" because a blocking assignment blocks execution of the next statement until it completes. Therefore the results of the next statement may depend on the first one being completed. Non-blocking assignment ...

Non Blocking Proceduaral assignments. The non-blocking assignment statement starts its execution by evaluating the RHS operand at the beginning of a time slot and schedules its update to the LHS operand at the end of a time slot. Other Verilog statements can be executed between the evaluation of the RHS operand and the update of the LHS operand ...

15.2.3 Non-blocking Assignments with Inter-assignment Delays. Using the intra-assignment delays with the non-blocking assignment, it delays both the evaluation of the assignment and the update of the assignment. Consider the Verilog code shown in Example 5.

I am posting this question after going through a famous presentation on "understanding verilog blocking and non-blocking assignments by stuart sutherland" which literally discusses every possible variant. Input 0-10 LOW 10-20 HIGH 20-30 LOW 30-33- HIGH 33-36-LOW 36-45 HIGH 45-end of simulation LOW For the 2 cases below my analysis is output follows input with the mentioned delay. so the ...

div_valid changes before the RHS of non-blocking assignment is evaluated; div_valid changes after the RHS of non-blocking assignment is evaluated #1 above leads to a behavior observed by you - both div_valid and var seem to change on the same clock cycle. #2 above leads to a delay of 1 clock cycle from div_valid to var change.

This has no affect on behavior as everything is executed sequentially. begin. @a // blocking event delay waits for a change on -a-. #1 // blocking time delay waits for 1 time unit. t <= a; // non-blocking assignment. // uses the current value of -a- one time unit after it changed. // and schedules an assignment to t.

Why does "non blocking" assignment in Verilog seem like a misnomer? Because it is a misnomer.. The term non-blocking was created as a corollary antonym to the prior misnomer blocking.. Better terms for blocking and non-blocking would be ordered evaluation and unordered evaluation or series evaluation and parallel evaluation.. But then there is a cruel twist: The ordered evaluation is ...